**JANUARY 2023**

# DESIGNATION OF THE PROPERTY OF

the ADVANCED future

## REALITY CHECK AHEAD

THE PRINTED CIRCUIT DESIGNER'S GUIDE TO.".

**Designing for Reality**

Learn how to create realistic designs and advance your skills!

**Download**

## DESIGNOUT NEW YORK NE

## **The Advanced Future**

The year 2022 might be remembered as the Year of Advanced Packaging. The Department of Defense got the ball rolling last summer with the CHIPS Act, and the IPC Advanced Packaging Symposium helped outline the hurdles we're facing with complex packaging. In this issue a variety of experts discuss the challenges and trade-offs that PCB designers and design engineers are seeing today with advanced packages.

#### **FEATURE ARTICLES**

- **Advanced Packaging Means** 10 **Advanced Routing Issues** by Kris Moyer

- A Challenge Facing 24 **Aerospace Designers** in 2023 by Lee Ritchey

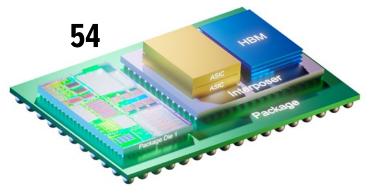

- **Scaling Beyond Silicon** 54 by Ashutosh Mauskar

- **FEATURE COLUMNS**

- **PCB Design and Advanced** 8 **Packaging** by Andy Shaughnessy

- Threading the Needle Through 28 **Advanced Packaging** by Tim Haag

- **Advanced Packaging** 32 **Not a Passing Fad** by John Watson

### **Don't Overthink Your Prototype Builds**

Go with the team that can make your ideas a reality...

RF · MICROWAVE · HIGH-SPEED · QUICK TURN EXPERTS

**Accurate Circuit Engineering** 3019 Kilson Dr

Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: **James Hofer** (714) 227-9540

www.ace-pcb.com

## JESIGNUUT.

#### **SHORTS**

- 23 At the Edge of Graphene-Based Electronics

- 43 Soft Touch Sensitivity

- Elementary, Mr. Watson: 47 The Art of the PCB

- PCB Designer Dave Graves 67 Passes Away

- A Greener Internet of Things **73** With No Wires Attached

#### **DEPARTMENTS**

- 77 Career Opportunities

- 88 **Educational Resources**

- 89 **Advertiser Index & Masthead**

#### **COLUMNS**

18 The Eye Diagram by Barry Olney

- 44 **Demystifying Multilayer PCBs** by Matt Stevenson

- 60 Automotive Conformal **Coating Applications** by Saskia Hogan

**A Patently Innovative Revolution 70** by Joe Fjelstad

#### **ARTICLES & INTERVIEWS**

**40** PCB Designers Are Really **Product Designers** by Zachariah Peterson

48 **Everyone Wants Change:**

Who Wants to Lead the Way?

with Alun Morgan and Mark Goodwin

**DFM 101—Final Finishes: HASL** 64 by Anaya Vardya

#### **HIGHLIGHTS**

- 38 MilAero007

- 68 Flex007

- **Top Ten Editor's Picks** 74

# Introducing EMA Support +

CircuitFit • Highlight Part • Find In Design • CIS Template-Based BOM • PCB Clustering

## Get more value for your maintenance with exclusive benefits from the PCB Design experts at EMA

Improve your productivity, solve problems faster, and work more effectively with access to EMA experts, training, and technology to optimize your Cadence design experience. All available for FREE to active maintenance EMA customers.

Learn More >>

## **PCB Design and Advanced Packaging**

#### The Shaughnessy Report

by Andy Shaughnessy, I-CONNECT007

It's hardly an exaggeration to say that 2022 might be remembered as the Year of Advanced Packaging. The Department of Defense got the ball rolling last summer with the CHIPS Act, which pointed out how far the United States has fallen behind the rest of the world

in microelectronics. A few months later, the week-long IPC Advanced Packaging Symposium took place in Washington, D.C., and I-Connect007 covered this event from start to finish.

Among the things we learned from the symposium: There's a great deal of innovation taking place in advanced packaging now, and it all starts with PCB designers and

design engineers making the correct decisions early in the design cycle.

When we started planning this issue, we wondered: What exactly do we mean by the term advanced packaging? IPC's Kris Moyer teaches a PCB design course on this topic, and he was kind enough to provide us with a twopronged definition of advanced packaging:

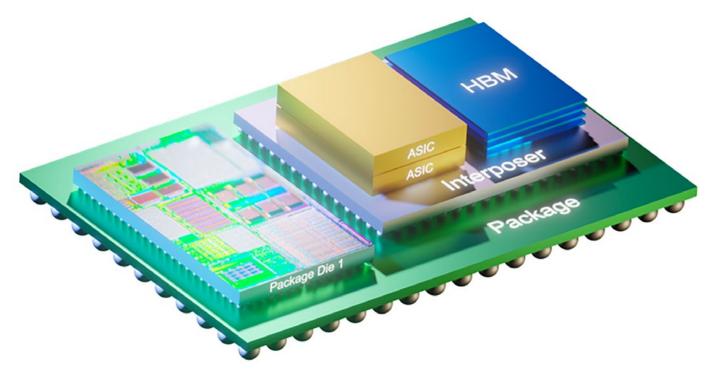

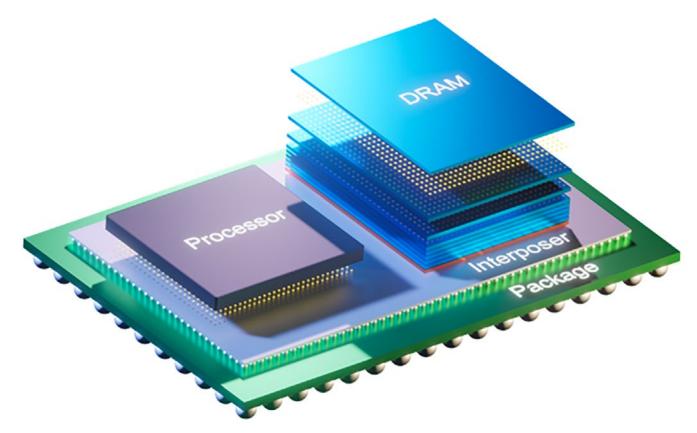

"The first definition is with respect to IC packages. For this, advanced packaging refers to the interposer boards that are made with advanced

> specialty materials, typically non-FR-4, along with advanced special manufacturing techniques and methodologies.

"The second is with respect to system/product design. For this, advanced packaging is a description of any advanced techniques and methodologies used in the design of PCBs for non-standard products. These include

sequential lamination and microvias used in HDI/fine-pitch products, chip-on-board/chipon-flex, direct wire-bond of bare silicon die to the board, non-standard board geometry, extreme reduction in board area, non-standard board mounting, etc." - Kris Moyer

Yes, even the definition of advanced packaging is, well, advanced. Every step of the design cycle is a potential trade-off that must be managed when working with non-standard PCBs. As we'll see with this month's features, the needs of the PCB designers and the designers of chips and packages are beginning to converge, and PCB designers now find themselves learning about chiplets and 3D-IC technologies. Will PCB designers of the future be experts at silicon interposer design?

We asked a variety of experts to discuss the challenges and opportunities that PCB designers and design engineers are seeing today with advanced packages, as well as trade-offs.

This issue leads with an article by Kris Moyer, who focuses on the routing techniques necessitated by advanced packaging. Next, Lee Ritchey discusses a challenge that's facing aerospace PCB designers who use stacked microvias, and he offers a variety of methods for circumventing this problem, including using staggered microvias. Columnist Tim Haag shares his take on designing complex packaging, and he tracks how complicated some designs have become over the past few decades.

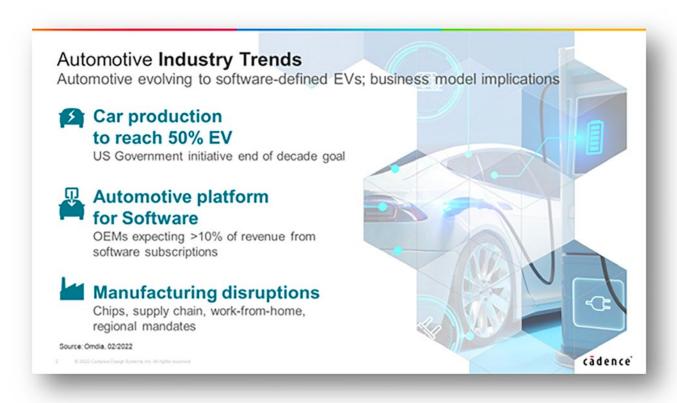

Ashutosh Mauskar breaks down nearly "perfect storm" of drivers affecting the semiconductor industry and packaging trends, including supply chain artificial intelligence, EVs and omous vehicles. And columnist John Watson explains why packaging is likely to continue shrinking and pushing Moore's Law to its limits: "We are simply running out of room."

We have columns from our regular contributors Barry Olney, Matt Stevenson, Joe Fjelstad, Anaya Vardya, and Saskia Hogan, as well as an article from Zachariah Peterson and an interview with Ventec's Alun Morgan and Mark Goodwin.

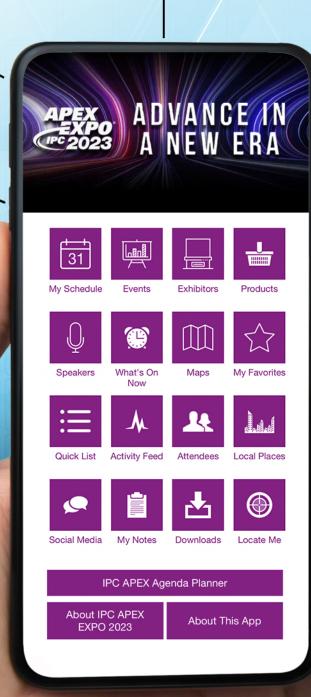

I hope you all had a great New Year's cel-ebration, and that 2023 is better than 2022. We'll be covering IPC APEX EXPO and DesignCon soon. I look forward to seeing you on the road. DESIGNOO7

Andy Shaughnessy is managing editor of Design007 Magazine. He has been covering PCB design for 23 years. To read past columns, click here.

#### Feature Article by Kris Moyer

IPC INTERNATIONAL

In today's ever-shrinking world of electronics designs, the use of BGA parts with very fine pitch features is becoming more prevalent. As these fine-pitch BGAs continue to increase in complexity and user I/O (number of balls), the difficulty of finding escape routes and fanout patterns increases. Additionally, with the shrinking of silicon geometry leading to both smaller channel length and increased signal integrity issues, some of the traditional BGA escape routing techniques will require a revisit and/or adjustment to allow for not only successful fan-out, but also successful functioning of the circuitry of the BGA design.

Historically, BGAs could be routed using traditional full through-via structures, with dogbone traces off the BGA pad. These BGAs were typically 1.27 mm in pitch and had sufficient clearance between the pads to place a Class 3 Level A via without violating any design rules. Additionally, the feature sizes of these packages were sufficient to fabricate in 1-ounce copper without any issues. With increases in chip complexity and I/O density, most BGA

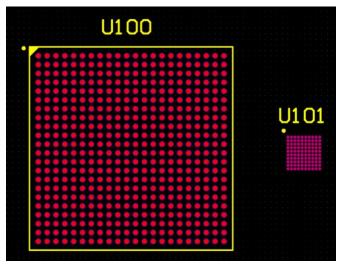

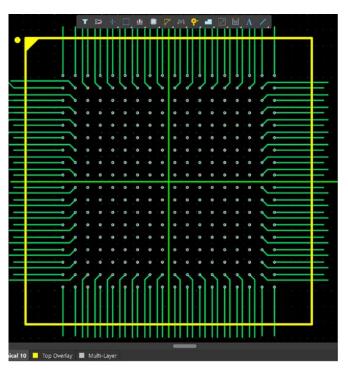

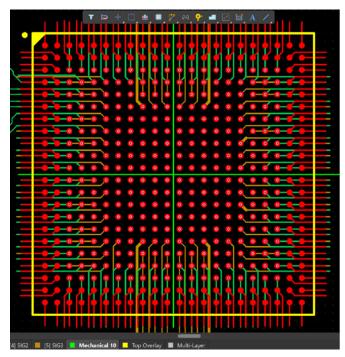

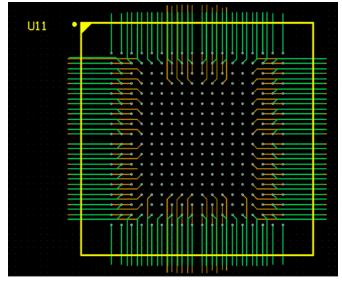

packages are now 1 mm or smaller pitch, with some packages as small as 0.4 mm pitch. With these finer pitch packages, it is no longer possible to use traditional full-thru via structures under the BGA. This, in turn, will require the use of sequential lamination and microvia structures in order to successfully escape route the BGA. Figure 1 shows a comparison

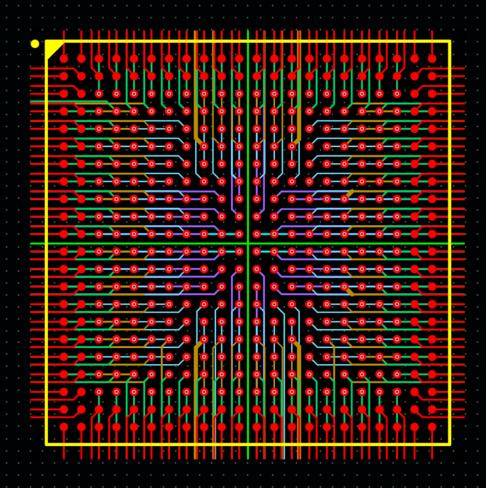

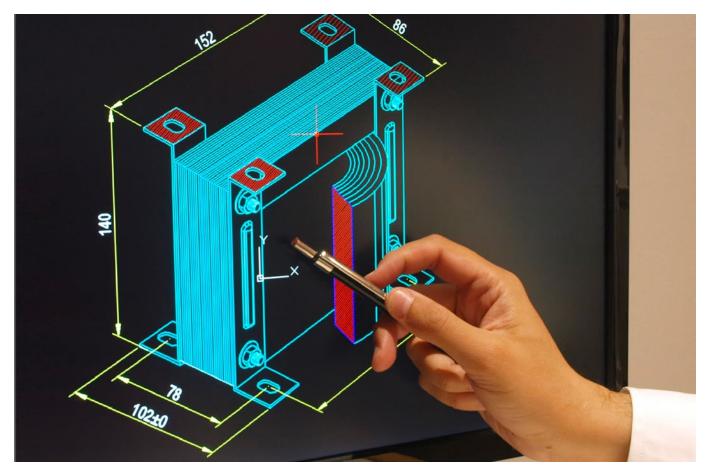

Figure 1: Comparison between the package and feature sizes of a 484-ball 1 mm pitch BGA (U100) and a 100-ball 0.4 mm pitch BGA (U101).

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 500 PCB experts on 3 continents speaking 19 languages at your service. Regardless where you are or whenever you have a question, contact us!

What's your PCB question? www.ncabgroup.com/pcb-design-mistakes/

Figure 2: A structure with every layer of a 28-layer board constructed as an HDI layer.

This is not possible with today's fabrication processes.

between the package and feature sizes of 484-ball 1 mm pitch BGA (U100) and a 100-ball 0.4 mm pitch BGA (U101).

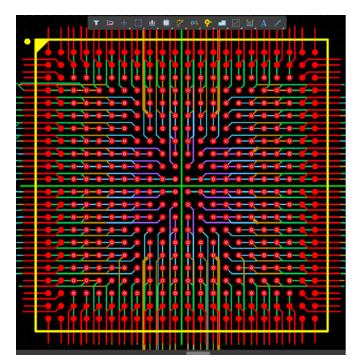

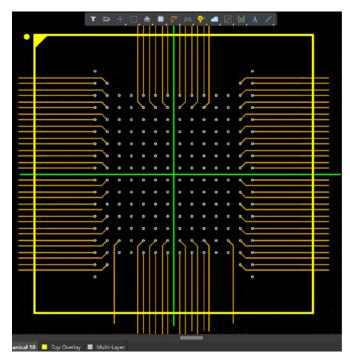

First, we look at the 1 mm pitch part, then evaluate what it will take to escape all balls to the outside perimeter of the BGA. For this evaluation, we will only consider the use of stacked microvias. Staggered microvias will also work, but require significantly more board area. Additionally, the stackup will assume dual stripline for all internal signal layers.

The first challenge in routing the BGA is to define how many HDI (sequential lamination/microvia) layers will be needed. Figure 2 shows a structure with every layer of a 28-layer board as an HDI layer. This, however, is not producible with current HDI fabrication techniques—more on this later.

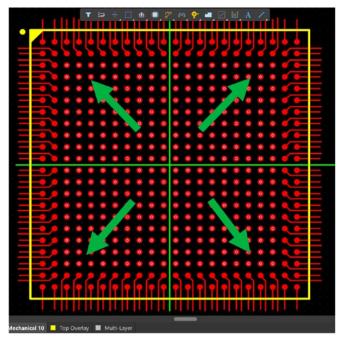

The basic technique to escape route the BGA is the quadrant method. With this method, we will divide the BGA into four quadrants and then use a standard pattern in each quadrant. Figure 3 shows the basic quadrant pattern.

Once the quadrants are defined, we will route the BGA in two-row patterns. The outside-most rows will be routed straight. The inside row will be routed in the direction of the quadrant, and then straight. Here the two outer-most rows will route on the top layer.

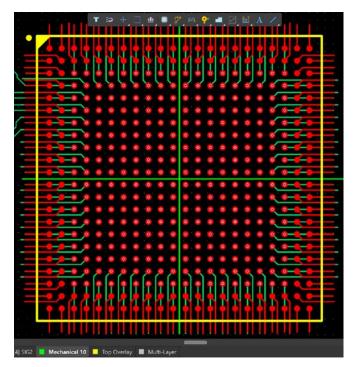

The next two rows will route on the first internal signal layer, and so on. Figures 4 and 5 show the routing of first internal signal layer.

Figure 3: A quadrant pattern used to escape route a BGA.

Figure 5: Routing of the first internal layer, continued.

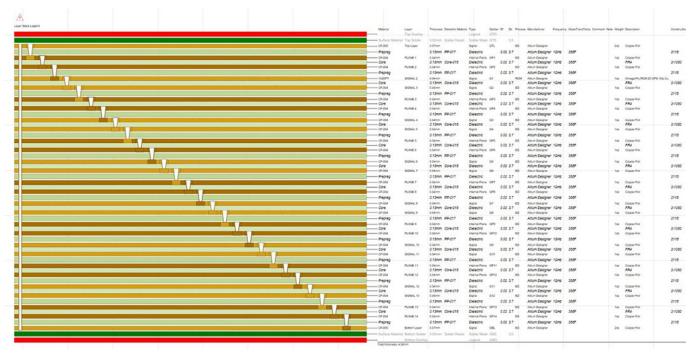

|   | Name          | Material      | Туре        | Weight   | Thickness | Dk  | Df   |

|---|---------------|---------------|-------------|----------|-----------|-----|------|

|   | Top Overlay   |               | Overlay     |          |           |     |      |

|   | Top Solder    | Solder Resist | Solder Mask | 1        | 0.8mil    | 3.5 |      |

|   | Top Layer     | CF 005        | Signal      | 2oz      | 2.756mil  |     |      |

|   | Dielectric 13 | PP-017        | Prepreg     |          | 5.1mil    | 3.7 | 0.02 |

|   | PLANE1        | CF-004        | Plane       | 1oz      | 1.378mil  |     |      |

|   | Dielectric 14 | Core-016      | Core        |          | 5mil      | 3.7 | 0.02 |

|   | PLANE2        | CF-004        | Plane       | 1oz      | 1.378mil  |     |      |

|   | Dielectric1   | PP-017        | Prepreg     |          | 5.1mil    | 3.7 | 0.02 |

|   | SIG2          | CF-004        | Signal      | 1oz      | 1.378mil  |     |      |

|   | Dielectric 15 | Core-016      | Core        |          | 5mil      | 3.7 | 0.02 |

|   | SIG3          | CF-004        | Signal      | 1oz      | 1.378mil  |     |      |

|   | Dielectric 16 | PP-017        | Prepreg     |          | 5.1mil    | 3.7 | 0.02 |

|   | PLANE3        | CF-004        | Plane       | 1oz      | 1.378mil  |     |      |

|   | Dielectric 17 | Core-016      | Core        |          | 5mil      | 3.7 | 0.02 |

|   | PLANE4        | CF 004        | Plane       | 1oz      | 1.378mil  |     |      |

|   | Dielectric 18 | PP 017        | Prepreg     | <b>N</b> | 5.1mil    | 3.7 | 0.02 |

|   | SIG4          | CF-004        | Signal      | 1oz      | 1.378mil  |     |      |

|   | Dielectric 19 | Core 016      | Core        |          | 5mil      | 3.7 | 0.02 |

|   | SIG5          | CF-004        | Signal      | 1oz      | 1.378mil  |     |      |

|   | Dielectric2   | PP-017        | Prepreg     |          | 5.1mil    | 3.7 | 0.02 |

|   | PLANE5        | CF-004        | Plane       | 1oz      | 1.378mil  | 3   |      |

|   | Dielectric 3  | Core-016      | Core        |          | 5mil      | 3.7 | 0.02 |

| 1 | PLANE6        | CF-004        | Plane       | 1oz      | 1.378mil  |     |      |

|   | Dielectric4   | PP-017        | Prepreg     |          | 5.1mil    | 3.7 | 0.02 |

|   | SIG6          | CF-004        | Signal      | 1oz      | 1.378mil  |     |      |

|   | Dielectric5   | Core-016      | Core        |          | 5mil      | 3.7 | 0.02 |

Figure 6: The first 12 layers of this sequence.

At this stage, it should be pointed out that the stackup being employed is one that is proper from a signal integrity point of view (more on SI later). Figure 6 shows the first 12 layers of the sequence. In this figure you see that you need three microvia transitions to transition from

Figure 7: Screen shot of another step in the sequence.

Figure 9: Escape routing screen shot illustrates the complexity of BGA routing today.

top layer to sig 2, the first internal signal layer, top-plane 1, plane 1-plane 2, plane 2-signal 2. This is due to a need for planes to act as shields between pairs of signal layers and the need for planes to be added as pairs to form planar

Figure 8: Escape routing sequence, continued.

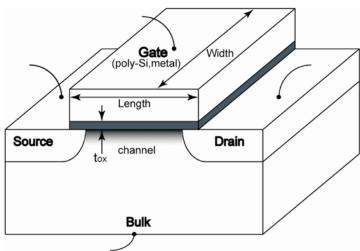

Figure 10: Two adjacent signal layers—a dual stripline structure.

capacitance to handle the high-speed switching current demand of the digital circuits.

Regarding some of the signal integrity issues that might be encountered using this technique, we will look at two adjacent signal layersa dual stripline structure (Figure 10). First, you will notice parallelism between the traces

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 500 PCB experts on 3 continents speaking 19 languages at your service. Regardless where you are or whenever you have a question, contact us!

What's your PCB question? www.ncabgroup.com/pcb-design-mistakes/

on the same signal layer, as well as traces on the adjacent signal layers of the dual stripline. The parallelism on adjacent layers is the bigger problem for signal integrity, as this can lead to crosstalk if the critical length is exceeded.

To understand this concern we must understand that critical length is half the transition electrical length (TEL). To understand this, we must understand that TEL is the distance the signal will travel on the transmission line (trace) during the time the signal is being actively driven. This is the rise time/fall time of the digital signal. To calculate the TEL we must determine the velocity of propagation on the transmission line, using the following equation.

$$\sqrt{D_k} = \frac{c}{v}$$

Equation 1

Where:

$D_{\nu}$  = dielectric constant

c = speed of light

v = velocity of propagation

Using a little algebraic manipulation, Equation 1 becomes:

$$v = \frac{c}{\sqrt{D_k}}$$

Equation 2

Now assuming a standard FR-4 with a Dk of 4.0 and using imperial units (inches), we get the following:

c = 983.6 x

$$10^6$$

ft/s

$\sqrt{Dk} = \sqrt{4} = 2$

v = (983.6 x  $10^6$  ft/s) / 2 = 491.8 x  $10^6$  ft/s

(491.8 x  $10^6$  ft/s) x (12 in/ft) = 5.901 x  $10^9$  in/s

(5.901 x  $10^9$  in/s) x (1 x  $10^{-9}$  ns/s) = 5.901 in/ns

From this we see that if our rise time/fall time is 1 ns, we have approximately 6 inches for our TEL, making the critical length of half TEL about 3 inches. From this we can see that we can very easily escape out of our FPGA without significant SI issues before we need to add our series termination resistors.

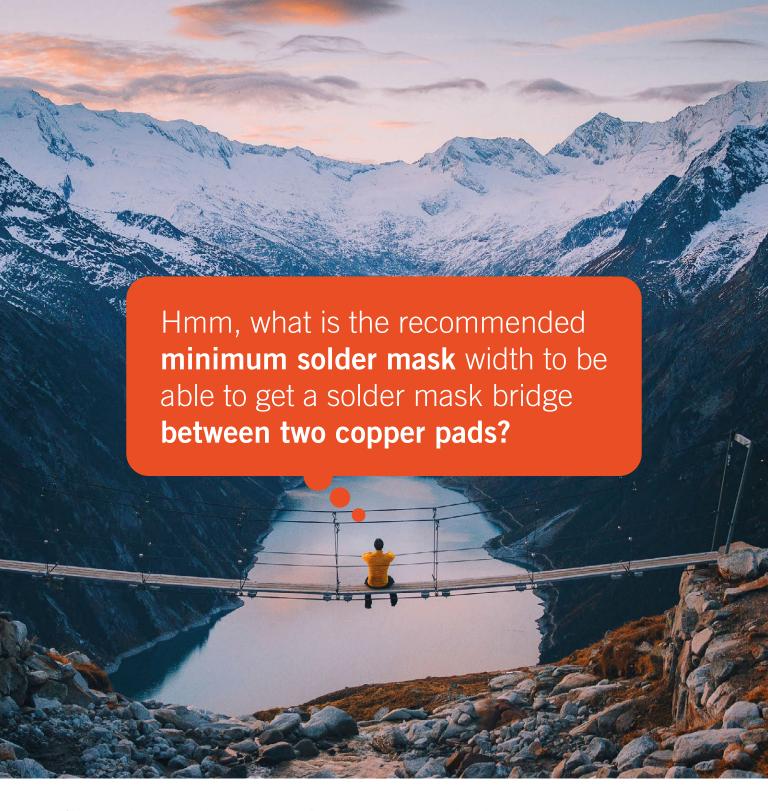

Modern FPGAs such as the AMD Xilinx Virtex UltraSCALE+ FPGA in 16 nm process have switching speeds as fast as 0.250 ns (Figure 11). From this, and by returning to Equation 2 again, we get a TEL of 1.475" and a critical length of 0.738".

Figure 11: Modern FPGAs have switching speeds as fast as 0.250 ns.

In next-generation devices that are being fabricated in process nodes of single digit nm channel lengths, we are seeing rise times/fall times of 0.1 ns (100 ps) or faster. This gives us TELs of about 0.6 inch and critical lengths of 0.3 inch or shorter. From this we can see that we can no longer expect to be able to route our FPGA traces outside the perimeter of the FPGA body before adding our series termination resistors for successful signal integrity performance.

To successfully solve this problem, the board designer will need to employ formed embedded resistors to the PCB structure. This technique uses a specialty layer of the PCB structure that has two different conductive materials on the same layer. One is the traditional copper, while the other is a resistive material such as nickel-phosphorous (Ni-P) that is used to create the resistors in line with the pins/vias of the FPGA/BGA ball.

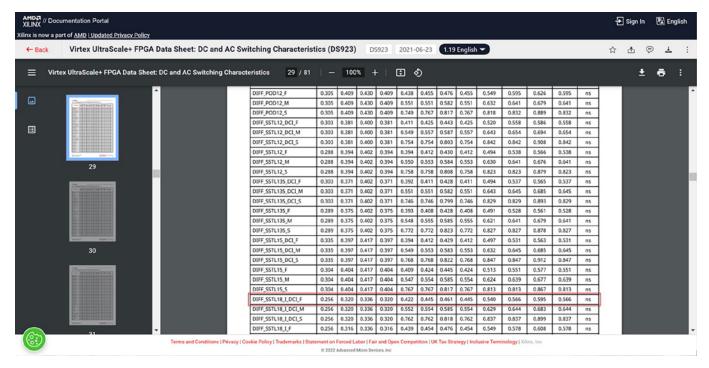

Now, to the question of process node: Process node refers to the length of the channel formed between the drain and source of a MOSFET by the gate of the MOSFET. Figure 12 shows an example of a traditional MOSFET structure. As the length of the channel gets shorter, the time it takes an electron to move from the drain to the source gets shorter (faster). This, in turn, is what leads to the faster and faster rise times/fall times in modern devices. This is also why we say that rise time/fall time and not clock frequency is the determining factor for when signal integrity rules must be applied to a design. But that is a discussion for a future article.

Regarding the issue of how to escape route out of modern FPGAs: After we incorporate the embedded resistor for the series termination we need for signal integrity, we still have the issue of crosstalk for the parallel traces on adjacent layers. The main technique to use is trace separation in the Z-axis.

In the event that you are not able to get a sufficient amount of separation/offset between

Figure 12: Schematic view of a surface channel MOSFET device indicating physical gate length, channel width, and physical gate dielectric oxide thickness (t ox)1.

the traces on the adjacent layers, it will be necessary to add additional plane layers to provide shielding/isolation between the trace layers. This approach has its own problems due to the need to add many layers to the board, which increases both mass and overall manufacturing complexity from the increased layer count, as well as the signal integrity desire to always add planes as pairs for Vcc/RTN both for planar capacitance for signal integrity and for proper Z-axis copper balancing for manufacturability. This too is a discussion for a future article.

As we have seen, with the reduction in package size and increase in device speeds, escape routing FPGAs/BGAs continues to pose significant challenges to the modern PCB designer. DESIGNO07

#### References

1. "Simulation study of scaling design, performance characterization, statistical variability and reliability of decananometer MOSFETs," PhD thesis by Xingsheng Wang at University of Glasgow, May 2010.

Kris Moyer, CID/CID+, is an IPC design instructor and chair of the IPC 1-13 committee.

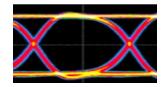

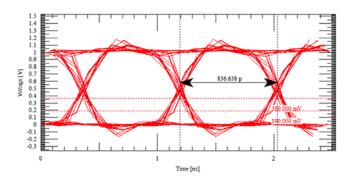

## The Eye Diagram

#### **Beyond Design**

by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

An eye diagram is a useful tool for the analysis of signals used in digital transmission. It provides a quick scan of system performance and can offer insight into the nature of channel imperfections. An eye diagram is simply a graphical display of a serial data signal with respect to time that shows a pattern that resembles an eye. Careful scrutiny of this visual display can give one a first-order approximation of signal-to-noise, clock timing jitter, reflections and skew. In this month's column, I will take an eye-ball look at the eye diagram.

An eye diagram overlays the signal waveform over many cycles. The stimulus is normally a pseudo-random bit stream (PRBS). Each cycle waveform is aligned to a common timing reference, typically a clock. An eye diagram provides a visual indication of the volt-

age and timing uncertainty associated with the signal. In an ideal world, eye diagrams would look like rectangular boxes. However, in reality, communications are not perfect, so the transitions do not align perfectly, resulting in an eye-shaped pattern.

A pseudo-random bit stream is a program that applies mathematical algorithms to simulate randomness. It generates a sequence of binary numbers, synchronized by a clock, approximating the properties of random numbers. The triggering edge may be positive or negative, but the resultant pulse that appears after a delay period may go either way. Therefore, when many such transitions are overlaid, positive and negative pulses are superimposed on each other. Overlaying many such bits produces an eye diagram. This sequence (up to

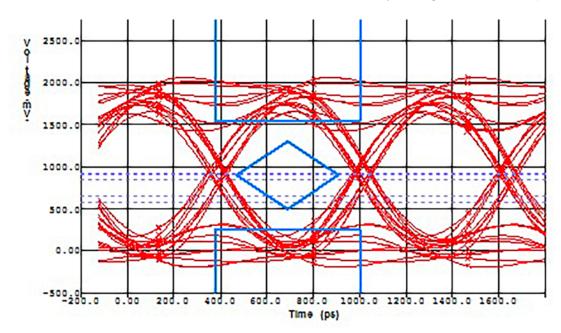

Figure 1: Eye diagram of a serial data stream with an eye mask.

## Standard To Advanced Technology

#### We're In It

#### The Solution is APCT

Technology | Cycle Times | Engineering Support | Offshore Solutions

- Technological Innovation

- Exceptional Cycle Times

- Comprehensive Engineering Support

Consistently Reliable Quality

- Complete Offshore Management

- Knowledgeable Technicians

Printed Circuit Board Manufacturer

**APCT.com**

1024 bits/s) is used to stimulate IBIS models in a transmission line configuration and, at the receiver, results in an eye diagramthat visualizes the signal quality. To get a quantitative view of signal integrity performance, other measurements can be applied to the eye-diagram pattern, including eye height, eye width, signal amplitude, comparative delay, slew rate and setup/hold times. The measured values can then be compared with the JEDEC specification.

The quality of a high-speed digital signal can be quickly determined by using a compliance mask overlay on the eye diagram display (Figure 1). A typical mask includes both time and amplitude limits. The blue area is keep-out.

The mask template can be configured based on the JEDEC specification, in which the middle section of the mask is made up of the setup/ hold time and stable voltage threshold specifications. Masks can also be customized to test certain specifications. By applying a mask test to the eye diagram, one can quickly tell if the signal can meet the overall signal integrity requirement. Unfortunately, mask dimensions are often difficult to determine from the specifications.

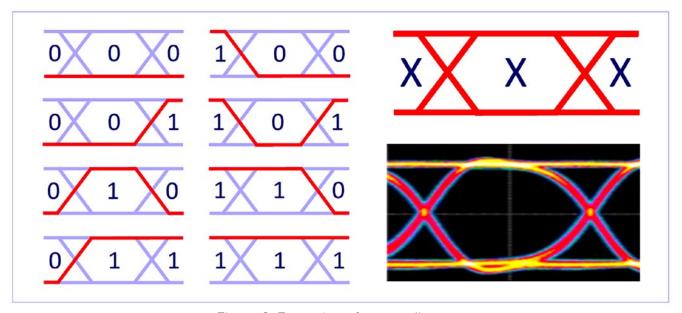

Eye diagrams include voltage and time samples of the data acquired at some sample rate below the data rate. In Figure 2, the bit sequences (left) are superimposed over one another to obtain the final eye diagram (right).

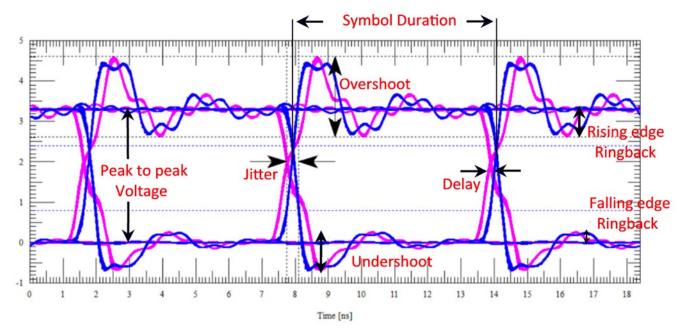

What an eye diagram (Figure 3) can tell us:

- AC timing noise or jitter, which is indicated by horizontal thickness

- AC noise or reflections, which is indicated by vertical thickness of the bunches

- The unit interval or symbol duration, which is equivalent to the center-to-center spacing of the crossovers

- The peak-to-peak voltage

- Overshoot and undershoot above/below the peak-to-peak waveform

- Whether the ring back is above or below the peak-to-peak waveform

- Rise/fall time, which can be measured from 10% to 90% of the rising/falling edge

- The comparative delay between two or more signals

Jitter arises when a rising or falling edge occurs at times that differ from the ideal. Some edges occur early; some occur late. In a digital circuit, all signals are transmitted with reference to a clock signal. The deviation of the digital signals as a result of reflections, inter-

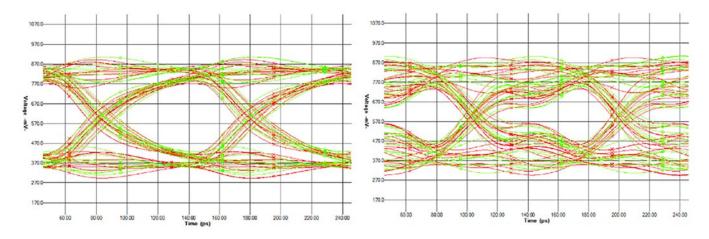

Figure 2: Formation of an eye diagram.

Figure 3: Eye diagram measures signal quality.

symbol interference, crosstalk, process-voltage-temperature variations, and other factors amounts to jitter. Some jitter is simply random.

The impact of termination is clearly visible in the eye diagrams generated. With improper termination, the eye looks constrained or stressed; with improved termination schemes, the eye becomes more relaxed (open). A poorly terminated signal line also suffers from multiple reflections.

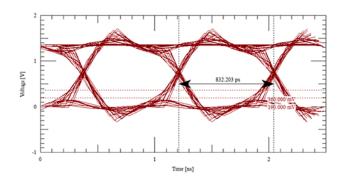

A practical way to analyze DDR signals is via the eye diagram. Either read or write DQ is folded into an eye based on the reference clock recovered from the DQS strobe edge. A composite eye diagram can tell the exact jitter content and distribution in your memory

interface, as the DQ signals are referenced to a clock (strobe signal). Additionally, it can display reflections from incorrect driver selection and on-die-terminations (ODT), as in Figure 4. Variations (reflections) at the peaks on the waveform indicate inappropriate termination.

Eye diagrams can also pickup stubs on highspeed serial links. Figure 5 shows the effects of excessively long via stubs on a high-speed differential pair. On the left, the differential pair is simulated using a pseudo-random bit stream with lossy transmission lines enabled—note the open-eye pattern. However, on the right, I have included via modelling, which enables the via parasitics and highlights the effects of via resonance. The high frequency harmonics

Figure 4: DDR3 data streams.  $40\Omega$  driver withno ODT (left);  $40\Omega$  driver with  $80\Omega$  ODT (right).

Figure 5: High-speed 10Gbps. Ethernet differential signal (left), and with via resonance (right).

are attenuated, rollingoff the signal rise time, distorting the signal, reducing bandwidth, and closing the eye.

Reflections are reduced dramatically by eliminating the stub. Back-drilling the via stub is a common practice on thick PCBs to minimize stub length for bit-rates greater than 3Gbps (1.5GHz). However, at transmission rates >10Gbps (5GHz), back-drilling alone may not be adequate to reduce jitter and bit error rate.

Eye diagram analysis is not the same as a bit error rate (BER) analysis, but the two techniques are often used in conjunction. The bit error rate percentage is calculated as the number of bit errors per unit of time. Bit synchronization errors are a factor, as well as distortion, interference, and noise.

The eye pattern is a composite signal that indicates the channel bandwidth, attenuation, jitter, reflections, comparative delay, and rise/fall time variations. Eye pattern measurements can show the overall signal integrity of a data path. They provide instant visual data that digital designers can use to check the signal integrity of a design and uncover problems early in the design process.

#### **Key Points**

An eye diagram provides a visual indication of the voltage and timing uncertainty associated with the signal.

- The stimulus is normally a pseudo-random bit stream. Each cycle waveform is aligned to a common timing reference, typically a clock.

- Overlaying many bits produces an eye diagram.

- The quality of a high-speed digital signal can be quickly determined by using a compliance mask overlay.

- The eye mask is made up of the setup/ hold time and stable voltage threshold specifications.

- Jitter arises when a rising or falling edge occurs at times that differ from the ideal.

- The impact of termination is clearly visible in the eye diagrams generated.

- A practical way to analyze DDR signals is via the composite eye diagram.

- A composite eye diagram can tell the exact jitter content and distribution in your memory interface, as the DQ signals are referenced to the strobe signal.

- Reflections at the peaks on the waveform indicate inappropriate termination.

- Eye diagrams can also pick stubs on high-speed serial links.

- Back-drilling the via stub is a common practice on thick PCBs to minimize stub length for bit-rates greater than 3Gbps (1.5GHz).

• Bit error rate is calculated as the number of bit errors per unit of time. DESIGNOO7

#### Resources

- "Beyond Design: How to Handle the Dreaded Danglers, Part 2," by Barry Olney, PCBDesign007 Magazine, Sept. 2016.

- "Fly-over Technology When It All Gets Too Fast," by Barry Olney, PCBDesign007 Magazine, Aug. 2021.

- "Eye diagram basics: Reading and applying eye diagrams," by Deepbak Behera, et al., EDN.com, Dec. 16, 2011.

- "What Is a High-Speed Eye Diagram?" by Texas Instruments Precision Labs, ti.com, 2019.

• Signal and Power Integrity – Simplified, by Eric Bogatin, Jan. 2019.

Barry Olney is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in board-level simulation. The company developed the iCD Design

Integrity software incorporating the iCDStackup, PDN, and CPW Planner. The software can be downloaded at www.icd.com.au. To read past columns, click here.

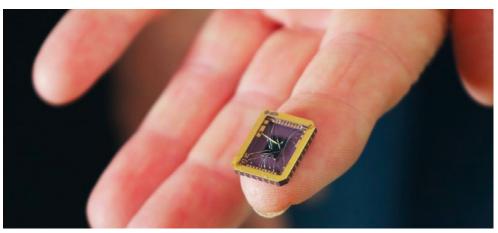

#### At the Edge of Graphene-Based Electronics

A pressing quest in the field of nanoelectronics is the search for a material that could replace silicon. Graphene has seemed promising for decades. But its potential faltered along the way, due to damaging processing methods and the lack of a new electronics paradigm to embrace it. With silicon nearly maxed out in its ability to accommodate faster computing, the next big nanoelectronics platform is needed now more than ever.

Walter de Heer, Regents' Professor in the School of Physics at the Georgia Institute of Technology, has taken a critical step forward in making the case for a successor to silicon. De Heer and his collaborators developed a new nanoelectronics platform based on graphene—a single sheet of carbon atoms. The technology is compatible with conventional microelectronics manufacturing, a necessity

for any viable alternative to silicon. Their discovery could lead to manufacturing smaller, faster, more efficient, and more sustainable computer chips, and has potential implications for quantum and high-performance computing.

To create the new nanoelectronics platform, the researchers created modified form of epigraphene on a silicon carbide crystal substrate. In collaboration with researchers at the Tianjin International Center for Nanoparticles and Nanosystems at the University of Tianjin, China, they produced unique silicon carbide chips from electronics-grade silicon carbide crystals. The graphene itself was grown at de Heer's laboratory at Georgia Tech using patented furnaces.

This process mechanically stabilizes and seals the graphene's edges, which would otherwise react with oxygen and other gases that might interfere with the motion of the charges along the edge.

It will likely be another five to 10 years before we have the first graphene-based electronics, according to de Heer. But thanks to the team's new epitaxial graphene platform, technology is closer than ever to crowning graphene as a successor to silicon.

(Source: Georgia Tech, photo credit: Jess Hunt-Ralston, Georgia Tech)

#### Feature Article by Lee Ritchey

SPEEDING EDGE

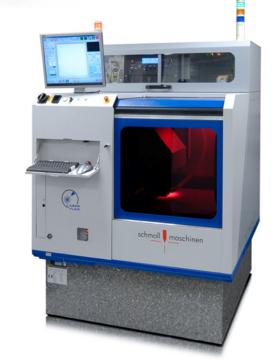

As the aerospace industry has been tasked with fitting increasingly complex electronics in existing airframes the demands on PCB substrates have begun to overtask the existing state of the art in PCB fabrication.

Recently, I was called in to troubleshoot some reliability problems with a very dense PCB that had components on both sides and required the use of stacked blind vias and buried vias. The usual name for this kind of design is "build-up fabrication," requiring many trips through the lamination, drilling, and plating operations at a fabricator.

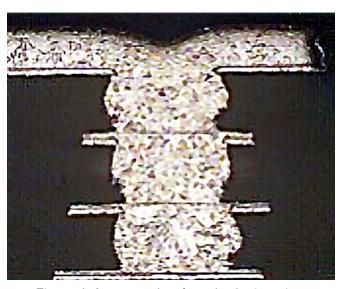

The designers decided to reach down from the outer layer to the third layer below the surface using stacked blind vias, much like that shown in Figure 1.

The process used to create the structure in Figure 1 is to fabricate a PCB using the ordi-

nary lamination, drilling, and plating processes employed for any multilayer PCB. Once this is done, a laser drill is used to create the

Figure 1: An example of stacked microvias.

### autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

Figure 2: Close-up of an unfilled laser-drilled blind via.

first blind via at the bottom of the stack as shown in Figure 1. As can be seen in Figure 2, at this point, the blind via has not been filled with copper.

To stack another blind via on top of the first one, the void must be filled with copper by employing an operation called "button plating." This results in tiny bumps of copper sticking up above the surface at each blind via. These bumps are removed by sanding to make the surface flat again. This is followed by laminating another layer of prepreg and copper thus creating a new outer layer.

The blind via laser drilling is repeated above the existing blind via and the plating steps are repeated to create the next blind via and then the third stacked blind via, resulting in a set of stacked blind vias like that shown in Figure 1.

The problem with reaching down to layer 3 is that the copper bond between the lowest blind via and the copper in the layer it attaches to is very weak. As the operating temperature of the device containing the PCB increases, the resin in all three laminate layers containing these stacked vias expands, pushing up on the copper pad on layer 1. This stress pulls the copper in the bottom via away from the layer it is in contact with, creating an open circuit.

When an assembly with this kind of defect is returned to the factory for repair, it has cooled off, the resins have contracted, and the circuit works properly. The assembly is returned to the field where it fails again. This process repeats until someone discards the assembly. Sometimes these PCBs are referred to as "rubber band" PCBs because they keep bouncing between the factory and the field as if they are

Figure 3: Staggered blind vias.

connected to the factory with a rubber band. Unfortunately, there is very little that can be done during fabrication to increase the bond strength between the bottom blind via and the layer it contacts.

But there is an alternative that can implemented early in the design cycle: The use of staggered blind vias as shown in Figure 3. Staggering vias precludes the above problems.

Engineers and designers from around the globe are looking into this problem, including the IPC's Weak Interface Microvia Failures Technology Solutions Subcommittee. But in the meantime, designers-particularly in the aerospace segment-should consider using staggered vias for complex PCBs like this.

With the demand for increasingly dense electronics in avionics and other military products, this kind of failure is going to appear more frequently unless designers find other ways to make connections deep into a PCB using blind vias. DESIGNOO7

**Lee Ritchey** is the founder of Speeding Edge and a signal integrity instructor who estimates that he has taught more than 11,000 engineers during his career.

## **ALL YOUR FLEXIBLE SOLUTIONS** IN ONE PLACE CatheterFlex™ Twenty Layer Rigid Flex Flexible circuit solutions Rigid flex solutions **CatheterFlex™** solutions Flexible heater solutions And assembly solutions too! And, Assembly Too!

#### **All Flex Solutions**

1601 Cannon Lane Northfield, MN 55057

(507) 663-7162 AllFlexInc.com

## Threading the Needle Through Advanced Packaging

#### Tim's Takeaways

Feature Column by Tim Haag, FIRST PAGE SAGE

Last week, my wife started a new sewing project that required a trip to the craft store for supplies, and she invited me to join her on this errand. This is not the first time I've faced this scenario: do I choose to follow her around the craft store pushing the miniature cart that will, by the time we get to the register, barely contain all her chosen fabrics and materials, or stay at home and watch TV? Thankfully,

by this point in my life I've learned which is the right choice, so we hopped in the car and headed down the road to the craft store.

I've been involved in electronics for a very long time now, and I am very familiar with the various manual and automated methods used for

PCB design, as well as the different tools and machinery used in their manufacturing. With this background, a simple project using needle and thread should be a cakewalk for me, don't you think? So—somewhat arrogantly, I must confess—I figured that my wife would ultimately benefit from my experience and expertise when it came to putting her project together.

Boy, do I feel like an idiot now.

The first thing that caught my eye in the craft store was an aisle loaded with assorted tools, where I noticed a selection of cutting instruments. Now I've always called them "scissors," but here was my first lesson of the day: Do

> you have any idea just how many types of scissors are used when sewing? The type of scissors you'll need is dependent on whether you are working with small fabrics, embroidery, or doublecurved embroidery. Then there are dressmaker shears, pinking shears, and tailor

shears. But before we're done, you also need to know about snips, heavy duty shop snips, applique, and of course, general purpose scissors. It doesn't stop there. You also need to know when to use serrated blades, non-stick coating, what kind of grip is best, which brands

## The fastest lead times in the US. Guaranteed.

#### We guarantee you the following:

- Your single-sided or plated through printed circuit board can be PRODUCED WITHIN 5 WORKING DAYS from the receipt of your PCB data.

- Your drilling data will be reproduced exactly both in position and diameter, improving assembly processes on your boards.

- Your printed circuit boards are inspected at 7 separate stages to ensure a perfect final PCB.

**Request a Quote**

mil-tronix.com

are recommended—and that's all just for the scissors. We could continue with a discussion on the whole line of rotary cutters, but let's escape from the sewing tool aisle while we're still young.

My wife expertly navigated her way through the various areas of the store, choosing between different fabrics, trims, and zippers. Next, she explored several different types and colors of thread, plus the bobbins required to install this thread in her own sewing machine. Buttons and interfacing had to be selected based on color, size, and durability. Just for kicks, we looked at patterns for potential future projects. However, all this took far less time than I would have expected because she had already planned how much fabric she would need, as well as how all the seams, hems, and stitching would be coordinated. Then she said something about a phone, and I thought that we were headed to the Verizon store next. Nope, she meant "foam," not phone, which was another unique yet crucial component of this project. Would you like me to tell you how many different types, styles, and sizes of foam there are to work with? I didn't think so.

Would you like me to tell you how many different types, styles, and sizes of foam there are to work with? I didn't think so.

By the end of the day, I had come to realize that my extremely naïve and rather arrogant perspective on my wife's sewing was completely out of line. She obviously has just as much—and probably a whole lot more—experience and expertise in the world of sewing as I do in PCB design. After following her around the craft store, I know that I would much rather

spend the day puzzling together some complex DDR routing than trying to understand how to sew. But isn't that the case with most things? There will always be those who have a greater amount of experience and expertise in a specific subject matter. To quote an adage: "There's always a bigger fish." An excellent example of this is the advanced packaging of PCB components, and how part selection affects the way we lay out a design.

When I first started designing circuit boards, components were less dense and more generic in both size and shape. I remember being told to leave enough room at the top of my throughhole 14-pin DIPs for a bypass cap. When I asked for the size, shape, or part number, I was told that it wasn't important; I just needed to create a generic part with a 0.4" x 0.1" rectangle using 62-mil pads spaced 300 mils apart from each other. They (whomever "they" were) would figure out later what to put in there, or they would just leave that part location empty. I wouldn't recommend using a relaxed component selection technique like that on a next generation smartphone design, as it probably won't get you many admirers.

Today, there are many component packaging variables that designers must consider when designing a board. Here are a few that come to mind:

- Functionality

- Power

- Price

- Availability

- Component life cycle

- Routability

- Human interface

Depending on the options, designers need to choose the part that will work best for their circuit, but they also must take into account the part's power needs and thermal issues, as well as whether the board design will support it. Before they can check off component selection on their to-do list, they also need to consider the part's price and availability, and

whether that availability will extend throughout the life of the project. Then they will have to verify that the component's footprint and density will work with the layer stackup and anticipated routing parameters. Lastly, the ability to manufacture, test, configure, rework, or manipulate the part by technicians and/or end users must also be considered. Yes, there's a lot to consider when choosing parts, and making a mistake can be costly.

One board that I designed many years ago had a new, unique through-hole connector placed in the middle that spanned almost the complete width of the narrow board being designed. This was a new part, and those that planned the interconnect strategy of the device had carefully chosen the connectors on the different boards for their size and pin density. The plan was to leverage the multiple layers of the board to route out of the connector, as well as to route all the other board traces between its pins. The problem was that the connector specifications called for a pad size that didn't allow for trace routing between pads, but no one had thought to check on this critical detail when the connectors had been chosen. By the time this design got into my hands, the mating connector had already been built into the other boards in the device—we were stuck. If memory serves, I think that we had to get a special exemption from our manufacturers just to build the board.

This story illustrates the importance of not only choosing the correct component for the application, but also the critical need for expertise in advance component packaging; without advanced packaging know-how, designers can't understand all the aspects and implications of using a new part. As I said earlier, component selection mistakes can end up being very costly in terms of manufacturing expenses and board failures. Yet as new and increasingly advanced PCB components become available, making these kinds of mistakes becomes more likely. While we would all do well to learn as much about component engineering as possi-

ble, it's important to identify resources that can help us understand the latest developments in advanced packaging and how they might affect component selection. One such resource is your circuit board manufacturer, who often has a full-time staff of component engineers to ensure that the best possible part choices are being made for their customers. Also, this edition of Design007 Magazine is full of insights from leaders in the PCB component packaging field on new technologies and how to make the best part choices.

The moral of the story is to not be ashamed to admit when you need help, especially when it comes to PCB component selection.

The moral of the story is to not be ashamed to admit when you need help, especially when it comes to PCB component selection. It may very well save you a lot of time, grief, and expense in the end. Today's advanced parts include high-density, fine-pitch BGAs that demand a well-thought-out layer stackup and routing strategy long before they are ever placed on the board. Just as my wife knew exactly what she needed from the craft store before she even got in the car, PCB designers need to know just how much we can and can't do with the parts in our designs—before we go to layout.

Until next time, keep on designing. DESIGNOO7

Tim Haag writes technical, thought-leadership content for First Page Sage on his longtime career as a PCB designer and EDA technologist. To read past columns, click here.

## **Advanced Packaging** Not a Passing Fad

#### Elementary, Mr. Watson

Feature Column by John Watson, CID, ALTIUM

We live in what can only be described as the golden age of electronics. Advancements and innovations grow by leaps and bounds, and never in history has the field of electronics grown at such a fantastic rate. Yet necessity is the mother of invention when discussing the PCB design industry and the advanced integration packages field is one of the fastest-growing and most exciting.

In 2020, the advanced packaging market was worth \$24 billion and it's expected to grow as the estimated compound annual growth rate (CAGR) is 8%1—phenomenal growth resulting from consumer demand. It's an insatiable appetite for something bigger and better, not only with higher speeds in a smaller package, but to be inexpensive; this is what drives our industry and keeps us employed. This demand is on full display when Apple releases its latest and greatest, and folks are camped out for days waiting for the release. This trend shows no signs of slowing down. One solution to high demand? Advanced packaging. As legislation with the CHIPS Act focuses on domestic semiconductor fabrication, the aim should be to increase the advanced package industry into the mainstream.

#### **Challenges with Advanced Interconnect**

Ever since Jack Kilby of Texas Instruments created the first hybrid IC made of germanium in 1958, and Robert Noyce created the first monolithic IC in 1959, the IC has generally remained the same—except for one significant difference in reducing the size of the transistors that make up every IC. When Kilby and Noyce created the first ICs, the size of the transistors was 11 nm. With today's smaller transistors, more nodes, as they are called, are now inside each IC.

By 1965, Gordon Moore estimated that a computer's speed and capability could expect

#### BENDING THE POSSIBILITIES

#### **AVAILABLE IN AMBER**

**AMBER**

- **Texact Exact Example 2** Excellent bendability

- Tigh Resolution by photolithography

- Tigh Reliability

- Simplified process

- **TUL94 VTM-0 certified**

- **1** Low spring back force

- **♥** Resolution Line/Space=50/50µm

- Solder mask defined opening (30µm diameter)

#### **OUR BIGGEST FLEX YET!**

Contact your local sales representative today!

Visit www.taiyo-america.com for more information.

to double every two years because of increases in the number of transistors a microchip can contain. It was a shocking statement when Moore announced that a single IC would someday hold 65,000 transistors. The size of IC nodes is now being mass-produced at 5 nm, which was commercially released in the Apple A14 Bionic chip. The transistor count now sits at a staggering 11.8 billion, a 38.8% increase from the A13's transistor count of 8.5 billion.

By 2024, the expectation is to be even smaller at 2 nm. For perspective, that is smaller than human DNA and could hold over 50 billion transistors on a chip the size of a fingernail.

But before we pop the cork on the champagne, I believe we have reached or very close to reaching the limits of our capability to produce chips reasonably and reliably. As things shrink, simply controlling the current flow in such a small area is very difficult. In other words, we are now getting so small that we can no longer control the electrons.

#### As things shrink, simply controlling the current flow in such a small area is very difficult.

We are simply running out of room. Many believe that Moore's Law is dead, particularly NVIDIA CEO Jensen Huang, who proudly announced his belief in this idea last year. I am not at that point yet, but it does feel like Moore's Law is on life support. Although we call it a law, even Moore agreed it was more of an observation. In his 1965 publication, Cramming More Components onto Integrated Circuits, he admitted that "the including micro-assembly techniques for individual components, thin film structures, and semiconductor integrated circuits. Each approached evolved and rapidly and converged." In an interview in April 20052,

Gordon Moore stated that the projection could not be sustained indefinitely: "It can't continue forever. The nature of exponentials is that you push them out, and eventually disaster happens." He also noted that transistors eventually would reach the limits of miniaturization at atomic levels:

In terms of size [of transistors], you can see that we're approaching the size of atoms which is a fundamental barrier, but it'll be two or three generations before we get that far—but that's as far out as we've ever been able to see. We have another 10 to 20 years before we reach a fundamental limit. By then, they'll be able to make bigger chips and have transistor budgets in the billions.

Another major problem we face is making all the interconnects to a high-density device so that it's a functional item on a PCB design. Conventionally it's done through wire bonds, which have not scaled down at the same pace as the transistor. With 11.8 billion transistors in a single chip, that is more processing power than wires can carry. Getting signals from the silicon out to the real world, which connects to the PCB, is a significant issue.

Frankly, we are reaching the industry limitations in more ways than one.

#### A Paradigm Shift of Advanced Packaging

Occasionally it's good practice to examine how we do things. Advanced packaging technology (APT) is a paradigm shift for the entire industry. It promises to solve the challenges we face. We can define APT as the aggregation and interconnection of components before traditional electronics packaging. Advanced packaging allows multiple devices (electrical, mechanical, or semiconductor) to be merged and packaged as a single electronic device. They are taking different circuits that were separate chips on the PCB design before and placing them all in a single chip.

Although we are not specifically talking about applications when speaking of APT, we will find

## PREMIER GLOBAL SUPPLIER to AUTOMOTIVE

FLEXIBLE CIRCUITS | EMS/ASSEMBLY | CONTRACT MANUFACTURING

**Industry leading Flex Design Support**

Flexible Circuits, Rigid Flex, Membrane Switches, Plastic Moldings

Specialized EMS/Assembly Services

EXPLORE the POSSIBILITIES!

Assemblies and Product Module Builds for Automotive

**IATF 16949**

Flexible Circuit Technologies 9850 51st Ave. N. | Plymouth, MN 55442 www.flexiblecircuit.com | +1-763-545-3333

that particular packaging methods are popular with various industries. For example, high-end AI products such as smartphones and graphic processing units lean more toward 2.5D technology. The industry demands target specific applications and markets with how the various individual circuits are combined with the packaging methods.

The various methods of advanced packaging are listed below.

- Wafer level packaging

- 5D and 3D

- System-in-package

- Bumping and flip-chips

- Chip scale packages

- Redistribution layers

- Embedded die substrate

- MESM and microsystem packaging

#### **Inherent Problems With APT**

The APT comes with several inherent problems. First is power dissipation and power use; directly connected to that is the increase and necessity of heat dissipation. Traditionally, silicon generates a lot of heat and is not thermally efficient. It is now seeing a decrease in voltages, but to maintain or increase the power means an increase in current. How is this power migrated through the package and the heat dissipated? Even just a single chip can have problems with power consumption and heat. Now we combine them with other items such as in a system-inpackage (SiP) that also holds the microprocessor, the flash, and the SRAM all in a single chip. We've just increased the issue exponentially.

#### **Known Good Die (KGD)**

When combining the various individual parts, especially when designing a SiP design package, It is unknown whether an individual circuit works until it is in the final package configuration. Because specific devices cannot be adequately tested beforehand, the failure rate is high and expensive due to lost production time. That is an issue known to the industry as

"known good die." How the individual dies are tested and validated must be solved. Usually, one only finds out about these issues after it's too late.

#### **Cost Issues**

Most integrated circuit manufacturers' equipment is not ready for the onslaught of advanced packaging. The equipment for such a process is highly specialized and expensive. This specialty requirement is driving up the cost of APT devices on the market. In the future, we should expect that costs should come down.

#### **Conclusion**

Advanced packaging technologies have a bright future. The insatiable appetite that the everyday consumer is looking for and expecting from their devices is increasing. It drives this new technology—one that is now mainstream as we finally put to rest Moore's Law and change how we look at the semiconductor industry with a major paradigm shift. Instead of simply looking at increasing node density, we can now customize based on entire sections of circuits for a specific industry and application. It's an exciting time. DESIGNOO7

#### References

- 1. Advanced Packaging Market Size to Hit Around US\$41.8 Bn by 2030," Nov. 10, 2021, GlobeNewswire.

- 2. "'Moore's Law is dead,' says Gordon Moore, by Manek Dubash, Techworld, Arpil 13, 2005.

John Watson, CID, is customer success manager at Altium, a professor at Palomar College, and an I-Connect007 columnist. To read past columns, click here.

Download the Altium eBook The Printed Circuit Designer's Guide to... Design for Manufacturing by David Marrakchi. You can also view other titles in our full I-007eBooks library.

IPC Community Magazine is an exciting, new, quarterly publication with a strong editorial focus on members' success. Coming in January!

# **KATEK Signs Purchase Agreement for** 100% Takeover of American Nextek

KATEK SE has concluded a purchase agreement with the owners of Nextek Inc., to acquire all shares in the US company.

# Jill Kale Appointed to Celestica's **Board of Directors**

Celestica Inc., a leader in design, manufacturing, and supply chain solutions, is pleased to announce the appointment of Jill Kale to its Board of Directors effective December 1, 2022.

# **Lockheed Martin Successfully Hosts Advanced 5G.MIL Capabilities on** Flight Ready Hardware >

Lockheed Martin, in collaboration with Intel, accomplished an industry first by successfully integrating a 5G Core and Open Radio Access Network into Lockheed Martin's 5G.MIL Hybrid Base Station.

# **BAE Systems, Purisolve Launch Promoveo Solutions Joint Venture**

BAE Systems and IT services company Purisolve, Inc. have combined forces to form a joint venture, Promoveo Solutions.

# Collins Aerospace Expands in India >

As part of a significant investment to expand its engineering, digital technology, and manufacturing operations in India, Collins Aerospace, a unit of Raytheon Technologies Corp., has officially inaugurated its new Global Engineering and Technology Center and Collins India Operations Center in Bengaluru.

# SAIC Awarded Approximately \$950M in **Space, Intelligence Contracts**

Science Applications International Corp. received approximately \$950 million in space and intelligence contract awards during the third quarter of fiscal year 2023.

# Smiths Detection Opens New UK Biolab

Smiths Detection, a global leader in the development of threat detection and security screening equipment, opened a biolab at its centre of excellence in Hemel Hempstead, UK.

# **NASA's Europa Clipper Gets Its Wheels** for Traveling in Deep Space >

Just as NASA's Mars rovers rely on robust wheels to roam the Red Planet and conduct science, some orbiters rely on wheels, too—in this case, reaction wheels—to stay pointed in the right direction.

# **Momentus Signs Contract with** Australian Research Centre >

Momentus Inc., a U.S. commercial space company that offers transportation and other inspace infrastructure services, has signed a contract with the CUAVA Training Centre at the University of Sydney to deploy the CUAVA-2 CubeSat in low-Earth orbit in October 2023.

# **Inmarsat Unveils Next-Generation Maritime Safety Terminal**

Inmarsat, a leader in global, mobile satellite communications, has unveiled a major innovation to its maritime safety portfolio: a next-generation terminal that will allow quick and easy access to industry-leading connectivity services.

America's Board Source

# PCB Designers Are Really Product Designers

Article by Zachariah Peterson ALTIUM

As I look back on 2022, I'm realizing that my company plays multiple roles in client projects beyond just designing circuits and PCBs. Sure, we're primarily a PCB design company, but we also help with things that happen outside the PCB. This includes tasks like enclosure design, defining mechanical constraints, simulating electrical behavior, mating boards into larger assemblies, selecting cabling, and defining test requirements, all of which slowly creep into the standard scope of work for design projects.

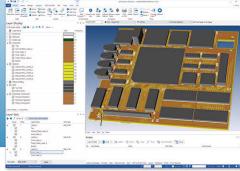

The same set of tasks have crept into CAD software features, especially in the PCB design space. Both mechanical design tools and PCB design software have expanded their capabilities beyond enclosure/fixture design and

board layout, respectively. Looking at some of the capabilities in a platform like Fusion 360, the MCAD side has significantly outpaced the ECAD side.

In the ECAD/EDA world, we still focus mostly on simulation and fit to enclosure, but there is so much more that goes into full-scale product development, and the ECAD software world should start to move much faster toward the goals I outline below.

# What PCB Designers Need for Product Development

As I mentioned in my earlier I-Connect007 article on simulation, designers need much simpler simulation access either inside their

Integrated Tools to Process PCB Designs

Quickly and easily specify the PCBs form, fit and function.

Use manufacturing data to generate a 3D facsimile of the finished product.

Visualize

Ensure that manufacturing data is accurate for PCB construciton.

Minimize costs in both PCB fabrication and assembly through maxiumum panel usage.

**Panelize**

CAM350°

Verify and Optimize PCB Designs for Successful Manufacturing

Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 | downstreamtech.com

©2019 DownStream Technologies, Inc. All rights reserved.

native PCB design tool or through a direct and seamless integration with another design/simulation program<sup>1</sup>. Now that ECAD/MCAD collaboration has helped bring electrical and mechanical co-design under one roof, designers can instantly pass ECAD data into the MCAD system and vice versa.

What else can the ECAD industry do to support product design? Based on both my personal experience with client projects and current ECAD industry trends, here are some things I'd love to see.

# **Cable and Harness Design**

This area is finally coming to fruition from my preferred EDA vendor, and I expect similar features from others. Many products, whether they are multi-board assemblies or requiring a connection to an external product, may do so with custom cables, custom or standard mated connectors, or flex ribbons.

Harness and cable definition at the logic level, visual integration into the assembly, and even physical design of custom cable assemblies—these are all essential parts of product development. The immediate benefit is in MCAD, where the connector and cable can be viewed in a larger system. However, the broader benefit is in simulation and rules checking, where logical definitions in interconnects are used to examine electrical behavior.

This takes a much higher-level view of systems design and eliminates the phenomenological modeling required in larger assemblies. For example, a harness-plus-cable model extracted from measurement or simulation could be used in SPICE to examine signal and power propagation across the interconnect before creating the PCB layout.

### **Embedded Development**

I continue to be surprised at the lack of support for embedded development by ECAD software vendors. I often make the joke to my ECAD/EDA clients that our industry has totally ignored embedded, and that we've

done this at our own peril. The closest we've come to supporting embedded systems development falls into three areas:

- FPGA system-level planning

- Embedded compilers targeting specific chipsets

- Version control

What we don't see is an integrated development environment (IDE) as part of a PCB design application, where users can create and manage libraries, their codebase, vendor libraries and code examples, reference design codebase, and a project's revision history. On the FPGA side, it would be wonderful if designers had the ability to see information a developer would see in the FPGA vendor IDE. We need this type of information to complete schematics for some of our most complex projects; being unable to see how IP can be implemented in our boards has led to redesigns, delays, and of course, cost overruns for the client.

# **Component Packaging**

In the future, I expect to see our industry shift its focus to different types of electronics assemblies, especially as length scales continue to shift smaller into UHDI. Here I'm referring to heterogeneously integrated components on substrates and interposers, where the designer takes control of the component capabilities and footprint.

In particular, I expect the packaging revolution to create a major shift in the way systems design teams approach new products, and especially the role PCB designers have to play in product development. IC substrates are basically just small circuit boards with very fine features; as the packaging market and heterogeneous integration starts to look a lot like the standard PCB market, PCB designers have the skills to immediately fill this product design gap.

It may take several years, or possibly a decade, for the traditional electronics design

process to get mirrored into substrate and packaging design, but I'm confident it will happen. This process is simply too big an enabler of advanced products at smaller scales to be ignored by the semiconductor industry, the big electronics distributors, and ECAD vendors.

### **Looking to the Future**

I expect to see more of the direct electromagnetics simulation integrations and system-level EDA features appear in ECAD software, continuing the trend we've already seen in recent years. Products from vendors like Keysight, Ansys, and others all play well with ECAD software, either through direct integration or a simple file export. The same goes for products like PTC Creo, Solidworks, and Autodesk, all of which have mechanisms to directly pass data with various ECAD platforms.

### References

1. "The Great Divide in PCB Simulation Software," by Zachariah Peterson, Design007 Magazine, July 2022.

Zachariah Peterson is the founder of Northwest Engineering Systems and a consultant for Altium.

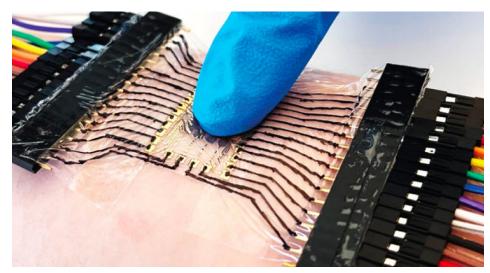

# **Soft Touch Sensitivity**

A soft and flexible electronic "e-skin," so sensitive it can detect the minute temperature difference between an inhaled and an exhaled breath, could form the basis of a new form of on-skin biosensor. The ultrathin material is also sensitive to touch and body motion, suggesting a wide array of potential applications.

"The skin plays a vital role in our interactions with the world," says Vincent Tung from KAUST, who led the work. "Recreating its properties in an e-skin could have profound implications for wearable electronics, as well as for sensory prosthetics, soft robotics and human-machine interfaces," he

says. Despite considerable research effort, however, it has been very challenging to create suitable materials, which must be strong and highly sensitive, yet imperceptible when applied to the skin.

Α carbon nanomaterial called hydrogen-substituted graphdiyne (HsGDY) could be ideal for the task, Tung and his collaborators have shown. This two-dimensional sheet of carbon atoms has similarities

to graphene in its strength and electrical conductivity, but also has key differences, Tung notes.

The team were able to show what the theory had predicted: the resulting material was highly twistable, stretchable and mechanically durable. "At around 18 nanometers thick, our e-skin is a fraction of the thickness of human skin, enabling conformal contact and long-term adhesion to the body with maximum flexibility and comfort," Tung says.

The material's island-bridge atomic structure not only contributes to HsGDY's soft and flexible nature but is also key to its electronic properties, Tung adds. (Source: KAUST)

# Demystifying Multilayer PCBs

### **Connect the Dots**

by Matt Stevenson, SUNSTONE CIRCUITS

As handheld and wearable technology become vital tools for industries ranging from health services to law enforcement, innovation increasingly coincides with PCBs getting smaller. For these devices, multi-layered PCBs offer requisite functionality for boards occupying a small space.

Multilayer PCBs enable more circuitry, components, and functionality to fit in a smaller space, as compared to single-layer or double-sided PCBs. Without them, miniaturization would be much more challenging and many of our coolest projects would rapidly become too clunky and unwieldy.

Though multilayer PCBs are becoming more common, many designers still have limited experience with multilayer board design. This can make the prospect of attempting such a design seem daunting, but multilayer boards do not have to be a hassle.

Just think of them as multiple single-layer boards stacked together.

Sound design processes for multilayer boards mirror that of single-layer PCBs: Choose the right CAD tool to optimize design capabilities and best support the transition from design to manufacture. Look for design tools

that will confirm design integrity and perform design rule

checks.

Following established best practices for design of multilayer PCBs means becoming familiar with multilayer design tips and guidelines provided by the CAD tool, gaining knowledge about tolerances and components unique to multilayer boards, and knowing the manufacturer's requirements for multilayer designs.

It is also a good idea to understand how multilayer boards are manufactured. The process, though complex, is easy to explain. Let's break

# Support For Flex, Rigid Flex and Embedded Component Designs Now Available. BluePrint-PCB CAM350

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

For more information visit downstreamtech.com or call (508) 970-0670

it down into a series of easy steps by looking at the assembly of an eight-layer PCB.

# 1. Grouping the Layers

The internal layers are grouped into pairs. For an eight-layer build, layers 2 and 3 are paired together, as are layers 4 and 5, and layers 6 and 7. What about layers 1 and 8? As they are on the outside, they'll be added later.

# 2. Imaging the Layers

These pairs are imaged together onto both sides of a copper-clad laminate core, creating three distinct double-sided inner layer panels. This image is a representation of the copper image defined by the electronic data for each copper layer.

# 3. Etching the Images

Once the layers are all imaged, they'll be etched. Etching removes the unwanted copper cladding, which creates spaces while simultaneously defining traces and pads.

# 4. Inspecting the Etched Layers

After etching is complete, the layers are inspected to ensure that etched images are defect-free.

# 5. Preparing for Lamination

The defect-free etched layers are then prepared for the lamination process using a chemical process that roughens up the copper to make sure it bonds to the prepreg.

There are several different names for this chemical process, including oxide, black oxide, and alternative oxide, to name a few.

# 6. Laying Up and Pressing the Layers

Once the oxide process is finished, the inner layers of the PCB are ready to be laid up and pressed into a single panel. A multilayer layup starts with preparing the lamination book. This book contains top and bottom plates made from steel, steel pins for alignment, thermal lagging material, stainless steel shims, PTFE release sheets, and, of course, the manufacturing panels.

# 7. Creating the Manufacturing Panels

The manufacturing panel is created by placing copper foil onto the alignment pins followed by prepreg layers. Prepreg is short for "preimpregnated," which refers to a partially cured glass-reinforced epoxy resin in sheet form.

The prepreg has two functions. First, it bonds the external foil to the adjacent copper layer and creates the dielectric insulator

| 6 Layer StackUp (0.062") L06-062-1oz1oz                   |                                                      | Thickness (inches) |

|-----------------------------------------------------------|------------------------------------------------------|--------------------|

| Layer 1                                                   | 1 oz foil plated to approximate* thickness 0.0024"   | 0.0024             |

| Prepreg                                                   | Bonding ply (2x2116) Average Dielectric Constant 4.5 | 0.0084             |

| Layer 2                                                   | 1 oz foil thickness                                  | 0.0014             |

| Core                                                      | Laminate Core Dielectric Constant 4.5 (+/- 0.10)     | 0.014              |

| Layer 3                                                   | 1 oz foil thickness                                  | 0.0014             |

| Prepreg                                                   | Bonding ply (2x2116) Average Dielectric Constant 4.5 | 0.0084             |

| Layer 4                                                   | 1 oz foil thickness                                  | 0.0014             |

| Core                                                      | Laminate Core Dielectric Constant 4.5 (+/- 0.10)     | 0.014              |

| Layer 5                                                   | 1 oz foil thickness                                  | 0.0014             |

| Prepreg                                                   | Bonding ply (2x2116) Average Dielectric Constant 4.5 | 0.0084             |

| Layer 6                                                   | 1 oz foil plated to approximate* thickness 0.0024"   | 0.0024             |

| "Thickness does not include soldermask or surface finish" |                                                      | 0.0636             |

between these layers. Prepreg comes in several thicknesses to help match the electrical requirements of the design.

Note that the copper foil in this step becomes the eighth layer in an eight-layer PCB design.

### 8. Applying the Layers

In this step, each etched and oxidized core is placed on top of the previous core's prepreg until the top layer is reached, where copper foil is applied again.

# 9. Assembling the Book

Finally, the completed layers are assembled into books. Depending on overall panel thickness, multiple panels can be contained within a single book. Separator sheets are placed between the panels to keep them from sticking together. In addition, shims can be added to evenly distribute pressure and maintain a consistent flatness across panels.

Thermal lagging material is generally placed between the steel plates on either end of the book and the first panel. This helps control the heat flow at a predictable rate into the manufacturing panels during lamination.

# **10. Pressing the Book**

Finally, using heat and mechanical pressure under vacuum, the prepreg is heated up and the epoxy liquefied in order to distribute it evenly. The epoxy then cools and hardens, bonding all the layers into a single panel.

The PCB is now ready to have holes drilled into and through it, creating a finished multilayer PCB.

Designing multilayer boards will become increasingly common, and it makes sense for designers of every experience level to become more familiar with best practices. DESIGNOO7

Matt Stevenson is vice president at Sunstone Circuits. To read past columns, click here.

### Elementary, Mr. Watson

# The Art of the PCB

by John Watson

After finishing the statue of David, Michelangelo—Italian sculptor, painter, architect, and poet of the High Renaissance—was asked how he had created such a beautiful work of art. He said, "The sculpture was already complete within the marble block before I started my work. I merely had to chisel away the superfluous material."

After decades of being in the industry and seeing countless designs, it's still amazing to see the exceptional beauty of a welldone PCB design. For designers, each PCB

begins as a blank canvas; not knowing what the final product will look like, we walk a fine line between engineering and artistry, often producing fascinating results.

There is a uniqueness to every PCB design. If I gave the same schematic to 10 individuals and asked them to complete the design, I can guarantee that each designer would come up with something different. This is a result of blending each person's understanding of engineering requirements with their own touch of artistry. From the very start of a project, there is a "flow" to the circuit in the schematic. With signals, best practice is to go from left to right, from inputs to outputs. With the powers and grounds, we move from the top down to the bottom. Seeing how different people interpret this process always makes me geek out a little, because in a PCB, we can clearly see evidence of the artistic tendency. There is a stunning beauty to the multi-layered colors and the various details of connections and features. such as length tuning, impedance matching, etc. It indeed can only be described as art.

To read the rest of this column, click here.

# Interview by Nolan Johnson

I-CONNECT007

Nolan Johnson recently met with Alun Morgan, technology ambassador at Ventec, and Ventec COO Mark Goodwin to discusses the industry's determination to cling to outdated processes and standards, and some potential consequences. To maintain efficiency and keep pace with the market's newest entries in Asia, Alun and Mark believe that legacy companies in the West must be open to challenging conversations that will require questioning old practices and revising those practices toward sustainability.

As Alun points out, everyone says they want change, but no one wants to lead the way.

**Nolan Johnson:** Would you say that there's an opportunity for innovation right now? Your options are to either stay inside old niches with low margins, or to start looking for new ways to do things. In another conversation, for example, you alluded to thermal management coatings as potential replacements for heat sinks. What other ways can you see this done differently?