# Industry 4.0: The Most Important Steps to Consider

Advanced Manufacturing in the Digital Age

**DOWNLOAD NOW**

and

## REAL MEwith...

EXCLUSIVE EVENT COVERAGE

### SMTAI 2020... virtual

The only place you can get exclusive interviews with show participants!

**WATCH NOW**

## SMTOOT MAGAZINE

## **Technology Roadmaps**

We reached out to a number of organizations doing roadmap work, as well as industry professionals volunteering during their personal time. What's clear is that creating a technology roadmap is not an easy task. This month (just in time for strategic planning), we talk roadmaps with those who make them and those who use them.

**IEEE's Heterogeneous** 14 Integration Roadmap, Part 1 Interview with Rita Horner

> Interview with **Paul Wesling**

42 The HIR Hits the Road With the **Automotive TWG** Interview with Rich Rice

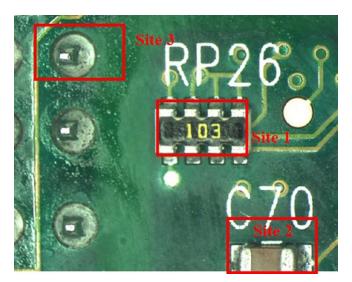

#### Significant Increase to Manufacturing Capacity - A Top Benefit

NK Technologies recently upgraded their manufacturing without a major economic expenditure. By taking advantage of Manncorp's Trade In, Trade Up Program, another MC389 Pick and Place was added to the production line used to assemble PCBAs for their current-sensing products, including the top-selling AG-series ground fault sensors (right). Read more

#### **Equipment Used in Production of NK Technologies' Ground Fault Sensors**

High precision, fully automatic stencil printer with dual-camera system TRADED IN

Pick and Place with 96 feeder ports and 10,500 CPH placement (2) MACHINES, TWICE THE SPEED

5-Zone inline reflow oven with flux management filter and predictive profiling

#### **CONTACT US!**

Chris (East) 215.869.8374 Ed (West) 215.808.6266 sales@manncorp.com

Hatboro, PA San Diego, CA FOLLOW US!

## SMT007 MAGAZINE

#### **SHORTS:**

- 17 Real Time with... SMTAI: Aegis Software 🔾

- 24 Lean Digital Thread: DFM Is Now as Easy as Spellcheck

- 56 Real Time with... SMTAI: Insituware 🗘

- 66 Real Time with... SMTAI: KYZEN 🗘

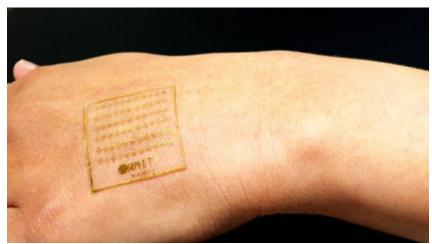

- 74 New Electronic Skin Can React to Pain Like Human Skin

#### **DEPARTMENTS:**

- 91 Career Opportunities

- 100 I-007e Educational Resource Center

- 101 Advertiser Index & Masthead

#### **HIGHLIGHTS:**

- 40 MilAero007

- 68 Market

- **76** Supplier

- **88** Top 10 from SMT007.com

#### **ARTICLES:**

50 Monsoon Solutions: Achieve Greatest Reliability With Optimized Panelization, Part 2 Interview with Jennifer Kolar and Dan Warren

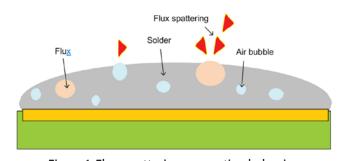

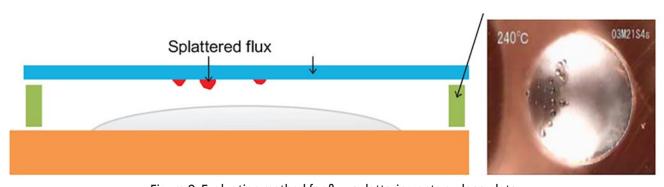

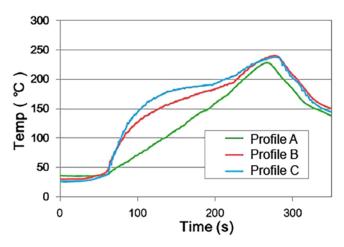

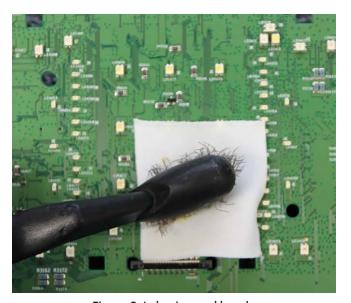

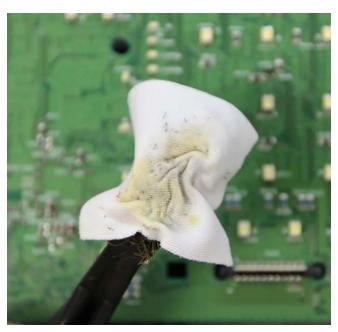

- 58 Reducing Flux Splatter in Sensors and Camera Modules by Jasbir Bath, Shantanu Joshi, and Noriyoshi Uchida

- 70 Programs for Veterans:

A Blackfox Update

Interview with Al Dill,

Jahr Turchan and

Sharon Montana-Beard

#### **COLUMNS:**

8 Roadmaps: Driving Into the Future by Nolan Johnson

- Joint Industry Standard IPC J-STD-006: Electronic Solder Alloys, Part 2 by Dr. Jennie S. Hwang

- 78 What's Lurking in the Shadows?

by Eric Camden

**84** Process Effectiveness Qualification by Alfred Macha

### We do it all:

From board Design and manufacturing throughout PCBA and Box Building. From s i m one or two sided boards to high complexity material Low, medium or high volume - whatever you need. With All we do we are meeting the HJGHEST standards requirements.

We offer an all-in-one solution through our experience, integrity, and clear communication. Get on board for the joint journey into the future:

### Roadmaps: Driving Into the Future

Nolan's Notes by Nolan Johnson, I-CONNECTOO7

Show anyone an image of travelers in the middle of nowhere, with a roadmap spread out across the hood of their car, and it's clear that they are lost. It's a universal symbol for a driver off course, consulting a map as a last resort. The implication is that roadmaps are only useful in an emergency.

This conclusion gives roadmaps a bad reputation. Roadmaps are navigational and predictive tools. Sure, they're also critical instruments when we find ourselves lost. But seasoned travelers and navigators use those maps to plan the journey, identify the milestones along the way, and know how to check that everything is still on course and on schedule, even when life throws obstacles in their path.

During a lecture I attended, Edward R. Tufte, a professor of statistical evidence and infor-

mation design at Yale University [1], shared an observation that Napoleon Bonaparte was so very successful as a military strategist because he had a unique gift for reading maps. Tufte suggested (and I'm paraphrasing liberally, using 20-year-old memories) that Napoleon's ability to visualize the three-dimensional reality of the terrain based on the 2D topographical representation meant that he could march, shelter, provision, and position his armies more expertly than his opponents. According to Tufte, Napoleon was a master of reading roadmaps.

With the unanticipated obstacles and changes in our lives that we've all faced and endured in 2020, I've thought almost daily about roadmaps, keeping a journey on track, and Tufte's anecdotes about Napoleon. If you

had any doubt that you should navigate your business to a roadmap in the same way that Napoleon moved his troops, I'd wager that 2020 has changed your opinion. It's best not to wait until you're lost to check your maps.

iNEMI recently released its 2019 Roadmap, and then IEEE announced the publication of the Heterogeneous Integration Roadmap (HIR). These were followed by an announcement that iNEMI and IPC would be collaborating on roadmap work in the future. We realized that October was the right time to discuss roadmaps across all three magazines.

We reached out to a number of organizations doing roadmap work, as well as industry professionals volunteering during their personal time. It became quite clear that creating a technology roadmap is not an easy task. The key difference between a technology and a traditional roadmap is that traditional roadmaps report on what has already been measured while technology roadmaps gaze into the proverbial crystal ball.

Ultimately, much of our roadmapping discussion came from our conversations with IEEE HIR participants. We start with two excellent overview features from Rita Horner of Synopsys and IEEE's Paul Wesling. Rita provides a conceptual walking tour of future markets with heterogenous integration that was so comprehensive we've broken her presentation into installments for all three October magazines. Paul's conversation detailed the motivations and purpose for the HIR and gave us insight into the process for creating such a futurist document. Then, we dive into detailed discussions with multiple committee members, exploring the details of some key chapters for PCB fabrication and board assembly folks.

There is more gold to mine from the HIR, as well as iNEMI's roadmap and the roadmap work of others. If you aren't already choosing and tracking your route to the future to at least one roadmap, we hope that this month's issue will help you to see why you should.

#### **Further Reading**

I highly recommend Edward R. Tufte's books, published by Graphics Press: The Visual Display of Quantitative Information (1983); Envisioning Information (1990); and Visual Explanations: Images and Quantities, Evidence and Narrative (1997). SMT007

Nolan Johnson is managing editor of SMT007 Magazine. Nolan brings 30 years of career experience focused almost entirely on electronics design and manufacturing. To contact Johnson, click here.

## **Looking to Hire New Talent?**

D.B. Management Group L.L.C. is currently working with a group of professionals who are seeking new positions.

## Joint Industry Standard IPC J-STD-006: Electronic Solder Alloys, Part 2

#### **SMT Prospects & Perspectives**

by Dr. Jennie S. Hwang, CEO, H-TECHNOLOGIES GROUP

#### Requirements for Electronic-Grade Solder Alloys and Fluxed and Non-Fluxed Solid Solders for Electronic Soldering Applications

This writing is a follow-up to the Part 1 column published in January 2020 that addressed the questions that had been raised regarding the joint industry standard. The specific questions were related to the lead-free alloy designations (a naming system) adopted in IPC J-STD-006 and the alloy designations expressed in Table A-1 of the standard, entitled "Composition and Temperature Characteristics of Lead-Free Solder Alloys." At the time of the revision, Table 1-A was essentially intended to be dedicated to new and existing lead-free alloys.

As the mid-year IPC Standard Committees meeting (SummerCom) was canceled as a result of the COVID-19 pandemic, I am using this space to address the questions. I will pri-

marily summarize relevant background information, the options for plausible naming systems, and the logic behind the decision to adopt the current naming system.

#### Background of Alloy Designation or Naming System

The revision J-STD-006B, published in January 2006, was the first industry-wide effort to include lead-free solder alloys in the J-STD-006 document. I was tasked to draft many parts of this revision, including Table A-1, by considering all available test data, opinions, comments, and historical and current information, as well as scientific principles and judgment.

We relied on several fundamental understandings and definitions:

- 1. A solder alloy is a mixture of elements in which the primary constituent is a metal.

- 2. The primary metal in an alloy is regarded as the base metal or the matrix.

#### Your American-Made Partner For

Bare Boards - Assembly - Turn-Key Box Solutions Experienced, Dependable, Affordable and Local

36-Years of Printed Circuit Board Production, Assembly and Manufacturing Expertise

Offering Bare Board, Assembled and Complete Turn-Key Box Solutions

84,000 Sq./Ft, Vertically Integrated World Class Facility

Millions of Controls Produced Annually

\$7-Million Dollars in New Automated Equipment in Last 12-Months

High-Volume Surface Mount and Through Hole Production Lines

Adherence to IPC Class 2 Standards or Higher

100% Optically Inspected; First Pass Yield Rate of 99.7%

**RoHS & REACH Compliant**

Globally Competitive Pricing

Quick Turn-Around Times Available

In-house Plastic Injection Molding Capabilities Available

In-House Hardware, Software and Product Design Engineering Services

Available

Extensive Component Library for Maximum Design Flexibility

Check out our Manufacturing Videos & Request a Quote Online at www.icmcontrols.com

Follow Us:

- 3. Minor elemental constituents, regardless of metallurgical nature (e.g., solid solution, discrete particulate, doping element, intermetallic compound-forming element), are considered non-base metal.

- 4. Minor elemental constituents, regardless of metallurgical nature (e.g., solid solution, discrete particulate, doping element, intermetallic compound-forming element), are considered either alloying elements or doping elements.

- 5. Inevitably, lead-free solder alloys fall in the Sn-based system (at least for the mainstream electronic packaging and SMT assembly industry sector.)

- 6. Individual companies and entities may have initiated their own naming systems or trademarks at their discretion. It is the companies' prerogative, for commercial purposes, to name solder alloys at their choice, which are formed independently from the list of Table A-1.

- 7. If needed, military drawings can be accommodated by an additional group of designations as a subset to reflect what have been used in the past in the electronics sector.

#### Options for Alloy Designation or Naming System

The task group has considered several options that were deemed plausible. Options included:

- 1. Following academic metallurgy, alloys are designated by element symbols, strictly, in alphabetical order (e.g., AgAuBiCuInNiSbSn).

- 2. Following the conventional practice or for practicality and convenience, alloys are named starting with the matrix metal, then followed with element symbols that are, strictly, in alphabetical order (e.g., SnAgAuBiCuInNiSb).

- 3. Some believe that noble metals should be listed first. Noble metals should be in alphabetical order first followed by

- non-noble metals in alphabetical order (e.g., AgAuPdPtBiCuInSb).

- 4. List by the order of electromotive force series. Indium is not classified as a noble metal (in electromotive force, In = -0.336 v; Ag = +0.80 v; Au = +1.42 v; e.g., AuPtPdAgCuBiSbIn).

- 5. Purely follow an alphabetical order of the name of elements in lieu of element symbols (e.g., antimony, bismuth, copper, indium, nickel, silver, tin).

With considerable deliberations and debates, and in view of the past historical practice and the forward-looking convenience, our task group then reached the consensus to use the naming system starting with the matrix metal (i.e., naming lead-free alloys by starting with Sn elemental metal). This is the genesis of today's lead-free alloy designations in J-STD-006 Table A-1.

#### **Future Work**

I hope that clarified the questions regarding the lead-free alloy designations being used in today's J-STD-006. Additionally, I want to take this opportunity to again mention the importance of future work for the task group to take on.

In our recent past meetings, I have challenged the task group to address four questions:

- 1. As a task group, how can we make the J-STD-006 document more useful, complete, informative, and practical for the industry, including suppliers, users, or other interested parties?

- 2. Which area(s) should be added?

- 3. Which area(s) should be expanded?

- 4. What are the priorities?

To this end, one recurring area that was brought up in our task group meetings was the differentiation and distinction between a dopant and an impurity. As more new alloys are being developed with intentionally added dopant(s) in a small weight percentage of the alloy composition, J-STD-006 bears the responsibility to provide a guide.

As stated before, the framework efforts should include updating solder alloy impurities and differentiating dopants from impurities. I have laid out the skeletal framework that is to be considered in three distinct categories of elements:

- 1. Current impurities elements (Table 3-2 of J-STD-006): Ag, Cd, Pb, Al, Cu, Sn, As, Fe, Zn, Au, In, Sb, Bi, and Ni.

- 2. Additional elements to be considered (phosphorus, sulfur, others). It is worth noting that QQ-S-571F (Federal Specification: Solder, Electronic) limits phosphorous (P) at 0.010 wt % and sulfur (S) at 0.005 wt %, but J-STD-006 makes no call on these two elements, which could potentially affect the properties and behavior of a solder alloy.

- 3. Dopants being used in alloys that are listed in the current impurity table as impurities (e.g., Ni, others).

To move forward to the next stage of the development of J-STD-006, these areas are to be addressed, which will call for collaborative efforts from both suppliers and users of the industry, as well as any interesting parties.

I would also like to take this opportunity to invite and encourage the industry colleagues to attend and participate in the task group meetings. The next in-person meeting, if feasible, will be likely held at IPC APEX EXPO 2021 in San Diego, California (time and date to be determined). SMT007

Dr. Jennie S. Hwang—an international businesswoman and speaker and a business and technology advisor-is a pioneer and long-standing leader to SMT manufacturing since its inception as well as to the development and

implementation of lead-free electronics technology. Among her many awards and honors, she was inducted to the International Hall of Fame-Women in Technology, elected to the National Academy of Engineering, named an R&D Star to Watch, and received a YWCA Achievement Award. Having held senior executive positions with Lockheed Martin Corp., Sherwin Williams Co., and SCM Corp., she was the CEO of International Electronic Materials Corp. and is currently CEO of H-Technologies Group, providing business, technology, and manufacturing solutions. She has served on the board of Fortune-500 NYSE companies and civic and university boards; the Commerce Department's Export Council; the National Materials and Manufacturing Board; the NIST Assessment Board; as the chairman of the Assessment Board of DoD Army Research Laboratory and the chairman of the Assessment Board of Army Engineering Centers; and various national panels/committees and international leadership positions. She is the author of 600+ publications and several books and is a speaker and author on trade, business, education, and social issues. Her formal education includes four academic degrees, as well as the Harvard Business School Executive Program and Columbia University Corporate Governance Program. For more information, visit JennieHwang.com. To read past columns or contact Hwang, click here.

#### **Upcoming Presentations**

Dr. Hwang will deliver a professional development course on "Preventing Manufacturing Defects and Product Failure" at the virtual SMTAI conference on October 5 (11:30 a.m.-3:00 p.m.). She will also deliver two courses at the virtual IMAPS International Microelectronics and Packaging Symposium on October 7 (3:00–5:00 p.m.) and October 8 (1:00-3:00 p.m.) on "Packaging/Board Integrity and Solder Joint Reliability" and "Prevent Product Failure: Tin Whisker and Intermetallic Compounds," respectively.

### IEEE's Heterogeneous Integration Roadmap, Part 1

#### Feature Interview by the I-Connect007 Editorial Team

This expert conversation focuses on the IEEE Heterogeneous Integration Roadmap (HIR)—a document that provides guidance for IC, PCB, and package designers, broken down by industry segment and performance requirements. Rita Horner of Synopsys shares her perspective from the IC side, as well as how the HIR might affect what happens on the PCB design and manufacturing side in the next few years. In Part 1, Rita provides a general overview of the HIR and its impact.

**Nolan Johnson:** Rita, can you kick us off by summarizing your background? Then, we'll shift into what the HIR means for PCB technologists.

**Rita Horner:** I have a master's degree in electrical engineering, and I spent about 10 years in circuit design, mainly transistor-level and mixed-signal design. I started with Hewlett-Packard, which spun off into Agilent. I left Agilent and then came back, which became Avago

shortly thereafter. I also worked at two startups. I have done mixed-signal designs. I was part of the Integrated Circuits Business Division of HP, where we designed the ASICs and IPs that were used by the different divisions within HP.

Then, I moved into marketing. I joined Synopsys about eight years ago. My focus was mainly on the high-speed interfaces until six months ago when I moved to the design group of Synopsys, focusing on the 3DIC Compiler product that we are developing.

**Johnson:** You have the right mix of background to have a good perspective on what's happening with heterogeneous integration. What trends do you see?

**Horner:** 3D IC is a hot technology. It's becoming hot because it has two angles: technology and economy. The semiconductor market has reached a point that the smaller technology nodes are not able to meet the required levels of integration with a single die in a single packaged part. The dies are getting so large that they're not becoming manufacturable.

While others struggle just to keep pace, we stay ahead of the curve by constantly investing in the equipment, people and resources needed to be the best total PCB solutions provider in the industry.

**VIEW OUR CAPABILITIES**

If you're familiar with the stepper sizes, there's a maximum stepper size that you can physically build a die to; it's about 800 millimeters square, limited by the reticle. When a die gets that large, the yields go down exponentially, which makes the part very expensive. You get only so many parts per wafer because of low yields. To make things worse, that maximum reticle size is not enough for the high level of integration that is

needed to bring everything closer together for the performance required by the cutting-edge applications, such as the AI accelerators and high-performance computing needs in the data centers and the high-end networking market. Combining multiple parts together in separate packages is not a practical option for these high-end products.

**Johnson:** That makes for an interesting conflict. You need to get all of that functionality onto the silicon, but it's hard to get that much functionality onto the silicon.

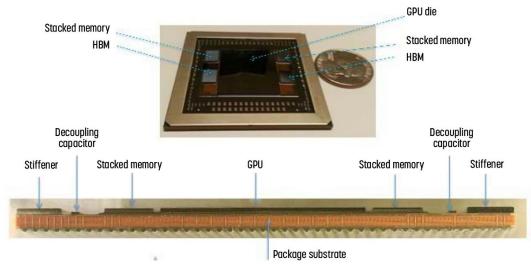

**Horner:** Exactly. High-end computing technology needs reduced latencies. This is becoming very critical because every time you make a hop from one packaged part to the next device to access data, you add latency. A lot of these AI applications require a lot of access to memory. And if you're making so many hops and going back and forth, the turnaround trip costs you a lot of latency, which is not very appealing because it means processing data will be slow. Bringing the memory closer makes more sense. That's why there's a big movement that started with AMD in bringing the DRAM memory much closer. As a result, JEDEC started the high bandwidth memory (HBM) standard a few years ago.

Effectively, there are layers and layers of DRAM that are stacked together, as a block of memory that can be attached to a processing unit. It could be a CPU, GPU, or any SoCs that need high levels of memory access with low latency. By putting those devices close to each

Rita Horner

other—especially in the same package, where you don't have to go out of the package, across PCB traces to another package to get access to data—you minimize a lot of latency and save power.

As far as the economic aspect of it, a complex design with mixture of lots of dies in a package consists of many layers of complexities that that need to be addressed. If there is a way to communicate information during package floor

planning to the SoC or the package designer, or the person who is going to assemble the part on a board, which could be beneficial to further optimize each part of the design, it could be optimized in parallel. Packages have many substrate layers, similar to the PCB layer concept, where having additional layers translates into increased cost. If you know, optimally, where to put the bump connections to the package substrate to minimize the number of substrate layers, or where to place the microbumps to make the most optimal die-to-die connection, to minimize the size of the interposer, these could translate to overall solution cost saving. There needs to be more communication between the package designer, the PCB designer, and the die designer for a cost-effective and optimal solution.

**Dan Feinberg:** 5G is accelerating that. One of the responses to this issue that you're discussing is the use of chiplets in CPU manufacture. Do you see that?

**Horner:** In many applications, it's not just because the die size is getting larger; it's also about when you have lots of parallel processing. At times, there are 40 + cores being processed in parallel inside a part. Looking at a few of AMD's designs, there are dies with four cores that are combined with four others of its own copy. That made it into four times four, so there are 16 cores within a package. When a large die is partitioned into smaller parts or for aggregating multiple cores, one has to decide on how to partition a die and what interfaces to use.

**Feinberg:** I just got through doing a build a few months ago with one of the new AMD chips, which is 24 threads. The challenge that I have, as a chiplet user, is temperature control. I had to go liquid cooling; it was not even a choice.

**Horner:** There are many challenges in multi-die package integration. Integrating multi-die in a package is not a new thing. It has been around for decades. In the past, there were very few devices that we were integrating, with very few connections between them. These were small designs compared to the multi-die systems in a package product that we see today. As more devices are included in a package, solution yield is reduced by the yield of each device multiplied. A single die in a package may have 99% yield, but then when you add one more device in the package, which may have 80% yield, you're talking about 80% times 99%, and your yield goes further down. By adding more devices, you're not helping the yield in that angle.

Different applications have various needs. That's why there are so many different types of interfaces. There are I/Os that require thousands of wires for one link connection. With the HBM interface for connection to the HBM memory stack, there needs to be 1,000 + dieto-die connections to one memory stack. In addition, these signals need to be shielded, which adds another level of complexities.

**Feinberg:** AMD is a leader in that area. I've always been kind of an Intel fan, but AMD seems to be leading. They seem to have gotten a good grasp on seven-nanometer geometries, where Intel is still struggling with anything smaller than 10 nanometers.

**Horner:** AMD no longer has their own internal fab. They depend on all their foundry and packaging partners. SMT007

Editor's Note: Stay tuned for Parts 2 and 3 in the October Design007 and PCB007 Magazines, respectively.

#### Real Time with... SMTAI: Aegis Software

Andy Shaughnessy speaks with Michael Ford, senior director of emerging industry strategy for Aegis Software, about its newest concept—Ontology—which the company will discuss during SMTAI. He also explains how Ontology relates to the company's existing MES products, as well as how it dovetails with the digital twin process. (View more at Real Time with... SMTAI 2020 virtual.)

## How the HIR Impacts Design Through Assembly

#### Feature Interview by the I-Connect007 Editorial Team

In this experts meeting on the Heterogeneous Integration Roadmap (HIR), the I-Connect007 editorial team met with Paul Wesling of the IEEE Electronics Packaging Society (EPS) to discuss what's in the HIR, where the organization is going with it, what the path is for the industry to have a roadmap like this, and how to use it in a practical sense.

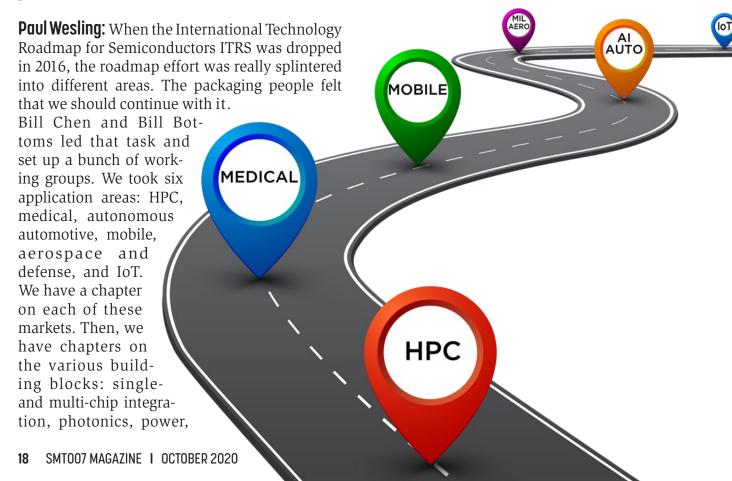

**Nolan Johnson:** There is quite a lot of future technology in the HIR that will affect PCB design, fabrication, and assembly. Could you fill us in on how the HIR project began and provide us with an overview?

MEMS and sensors, and all of the 5G, analog, and mixed-signal stuff.

For the underlying technologies, we have a chapter on each of these, such as research materials and devices. A large section on future devices, such as carbon nanotubes, is from the Electron Devices Society (EDS). There are also small sections on supply chain and security. These are big issues across much of our IP, especially when there are various breakthroughs in the supply chain companies around the world, doing different things with PCB design, testing, integration, etc. We also cover thermal management, co-design, and simulation. How do we find CAD/EDA systems that will integrate from the transistor model all the way up to the PCB and the system level and pass information

## The right solutions happen when you care enough to ask the right questions.

#### INTRODUCING: TECH 2 TECH

High-tech, high-value cleaning answer made easy

At KYZEN, we have the SCIENCE and expertise to solve any cleaning problem, and the CARE to find the perfect solution for your individual cleaning process. When science and care converge, your cleaning process succeeds on every level.

Sign up for a session today at Tech2TechbyKYZEN.com

KYZEN.COM

WORLDWIDE ENVIRONMENTALLY RESPONSIBLE CLEANING TECHNOLOGIES

back and forth, as opposed to doing it in silos today? We still have the same problem there.

Finally, there are three technological areas. Perhaps the biggest focus areas are system-in-package (SiP) options, and where that's going over the next 10–15 years: 3D and 3D interconnect, and wafer-level packaging at the wafer-level, fan-in, and fan-out. It also covers module system integration and different substrates. That's my quick overview.

**Johnson:** How can people access it?

**Wesling:** On our website at pwesling.com/hir, you can pick out any chapter. In addition, there is a PDF of the full roadmap (>600 pages), or you can unzip it on your machine and have it locally with a full text search, which is kind of handy. It's the way I structure conference proceedings. You can also find a video overview that was prepared for ECTC and broadcast in June; it's a six-hour webinar with an index. For example, if you want to see what's going on with single- and multi-chip packaging, you can skip to the 176th minute, which will show a 10-minute summary by the head of that working group. We also have nine one-hour video overviews of many of the chapters that are more indepth, and we're still working on similar videos for the other chapters.

**Johnson:** Some portions of the HIR directly apply to PCB fabrication; not all of them do, but some come pretty close. How is this roadmap intended to be used by the industry?

Wesling: There are four different groups that we see using this. First, research labs that need to look into the 10-year or 15-year period could use it. As we find out what they're doing, then we can reflect it every year or two in the roadmap and see what's integrating with other stuff. Second, the academic community could review it as well, such as Ph.D. students, depending on the projects on which they're working. Third, corporations that are either suppliers to this or users of it will want to keep an eye on it. They don't want to end up down a blind alley somewhere, working on

**Paul Wesling**

a technology that does not seem to be getting support. Fourth, technologists can use it to ask, "Where should my career go in the next 10 years? If I'm working on high-level PCBs or things like that for power electronics, where do I see that integration for automotive electronics and 400-volt power distribution? Where is that going?"

We monitor these four communities because that's who could use this roadmap. Our next roadmap is supposed to come out soon. This is a large group of volunteers. But the idea is that we'll take the pre-competitive information that we can glean from our 400 or so volunteers and put it into updated roadmaps with, for example, new projections and issues with line width, or whatever it is we're tracking, and where it's going. We see it working for those four communities and being an interactive resource that's freely available, so we hope it gets passed around.

**Johnson:** A lot of information on the roadmap tends to be related to integrated circuits (ICs), which makes sense since much of the technology is now inside the packaging.

**Wesling:** It involves the chiplets and higher levels that are up and down the stack (Figure 1).

**Johnson:** Since our readers are primarily attuned to PCB manufacturing, how is the technology in the HIR going to change what happens on the PCB?

Wesling: First, I want to address co-design and simulation. We expect that instead of finding local maximums or optimization for IC layout and then having to have a lower level of optimization at the board level and system level, we hope to trade off across the whole stack of technology. We expect PCB people to be working backward with the IC and chiplet design. It will be a challenge for CAD/EDA companies to provide the tools. Figure 1: Intel Agilex FPGA Chiplet

application. (Source: Intel) Andy Shaughnessy: That's a fundamental change in how you do your job, who vou communicate with, and what you communicate to them.

Happy Holden: We can't depend on Moore's Law any more. With five to seven nanometers for gate geometry, we're not getting all of our future gains by going to one nanometer, 0.1 nanometers, and 0.001 nanometers. The alternative would be putting multiple chips together in a different material, in some fashion, to make these future gains in performance and lower cost. It's not going to just be the single chip with all the horsepower of that single chip.

**Wesling:** We expect single chips to keep picking up more parts of the system, but the thermal and design and interconnect limitations aren't going to make that possible—except for special cases, high volume, or something like IoT. We expect to see better optimization. The board-level people must have models that can be extracted and pushed down to the chiplet level and the interconnects and the wafer-level processing stuff. There may be better models needed at the PCB level.

Testing is likely to change a lot. We hope to have a lot of known good die since it will be difficult getting access to things without having to scan in or scan out for all the parts at the board or the system level. There's going to be a testing issue, which is covered a lot in the test chapter. It may prove difficult for the board-level people to move to new materials, different interconnect speeds, different intra-process testing, etc. Intel® Agilex™ FPGA

Dan Feinberg: You mentioned chiplets quite a bit, which is relatively new. When do you recall chiplets first becoming commercially available in relevant places?

Wesling: Two years ago, I remember the DARPA thrust on chiplets. We would call them individual chips or subsets. Our roadmap covers both. We've adopted the idea

that you have a bunch of chips and a bunch of passives, such as inductors and capacitors, and then make your system with interconnects.

**Feinberg:** Advanced Micro Devices (AMD) was the one that made great use out of it. They went from a lap behind Intel to a totally different racetrack because of chiplets. There are a lot of other uses for it, but what would you think is the driver? For me, the driver of chiplets has been the move toward 50- and 100-thread CPUs.

**Wesling:** Lisa Su, AMD's CEO and president, highlights that. It was their earlier generation, which we cover in the roadmap, that split that big chip into four chiplets to spread the power to make interconnect better and hook it up to memory better. That was an excellent application and probably the first major one we saw.

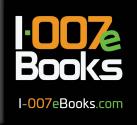

Aerospace and defense think chiplets will be their salvation for building systems because they can't build SOCs; they may only build 200 of their design. They need to use commercial chiplets and make their systems using your interconnects. Chiplets may become a moderately-used term, but we may also call it other things.

**Holden:** For me, this is an old topic because by 1972, we were putting multiple gallium arsenide LED dies on a PCB and wire bonding them over for second-generation calculators and things like that. Everybody thinks this is a 21st-century technology, but most of them aren't aware that back in the early '70s, we were doing a lot of chip-on-board and multiple chip-on-board.

**Wesling:** If you read chapter eight, you'll see that we still see wire bonding as a high-use application for bonding chips, three- and four-layer tiers, etc. Wafer-level packaging and flip chip may be coming in, but there's still going to be a lot of wire bonding.

Johnson: Happy's comments harken back to a time when all manufacturing took place at the same company. And because it was all under one roof, you could develop your own protocols and communications. It's different now. The various functional roles are fulfilled by third-party specialists. The need to communicate with multiple OEMs at the manufacturing level about this very detailed information is critical. For the PCB manufacturers, this technology could be the point where, no matter how well our systems work, they're going to break.

**Wesling:** That's why we've put in a supply chain chapter, which is not too developed, but we'll soon have one that's more extensive. One pain point is when only one company follows a standard. If we look back in five years to what we've published now, part of what we publish will not have been adopted. These are not standards; these are options for companies, consortiums, and university teams to get together and see if it works. Consequently, you'll see lots of potential solutions. Probably only a few will get implemented.

The other thing is in the supply chain. Our supply chain is spread out. Somebody does design, somebody does fabrication, and somebody else does assembly. This becomes a challenge in both supply chain and security. Look-

ing into the crystal ball and knowing what will happen is the tough part. That's why this roadmap extends to about 600 pages because it covers lots of possibilities—not all of which are going to happen—that can keep people in jobs for the next 10 years, for example.

You want to look at how it affects what your focus is, which is substrates and PCBs, and—more specifically—do they go away and get replaced by some other multi-chip substrate? Does polymer end up going somewhere? Does low-temperature processing start coming in here? What kind of things do you see that you can pull out of here that might be interesting? Once you get some draft ideas, you might kick them back to the people in the working group—because they're all listed at the end of the chapter—and say, "I'm thinking this. Is that still what you're thinking?"

This morning, I thought, "This is going to be about setting the ground rules and projections, and then every few months, coming up with something else—either digging more deeply into something that wasn't covered before to say what could happen or correcting what you thought earlier." Over the next months, we hope to have many of the updated chapters out for the 2020 version. Several of the chapters are being fully rewritten, but most of them are just being updated.

**Johnson:** The change to heterogeneous integration and the use of chiplets really is based on using an interposer, which ties together unpackaged chips into a system. Is that basically a PCB inside the system-in-package (SiP)?

**Wesling:** Yes. It's between silicon and the next level—the interposer (Figure 2).

**Johnson:** The interposer employs an interconnect design methodology—more than you would normally use in an active piece of silicon. Does that mean that PCB designer experience is going to be valuable on the wafer design side? Do the design tools need to change?

**Wesling:** Things like that are analogous to what PCBs have done in the past but at much higher

## Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Power Electronics

High-Speed Data

Automotive Electronics

Lamination

Startups

Our technology produces what our customers dream!

Figure 2: AMD Fiji GPU-HBM Si Interposer 2.5D Package. (Source: ASE)

densities. My guess is that the design function is going to be subsumed by the system-level packaging and substrate people rather than the PCB industry.

**Holden:** We don't have a roadmap, but it is also important to emphasize the other end of the spectrum. I believe in disposable electronics and printed electronics, such as a wristband that you can throw away when you're done using it. It would be made out of paper but designed with a five-cent chip to communicate with my smartphone and collect the information my doctor wants. Then it would upload data to AI that makes conclusions and tells my

doctor to give me a call to come in if it doesn't like what it's seeing.

**Wesling:** It's printed roll to roll and extremely cheap, almost like a newspaper.

**Holden:** That's where some of our people in PCB manufacturing or flex will decide to invest in that part of the developing market.

**Johnson:** Thank you for your time, Paul. I hope you had a great time.

Wesling: This has been fun. SMT007

#### Lean Digital Thread: DFM Is Now as Easy as Spellcheck

by Sagi Reuven

SIEMENS DIGITAL INDUSTRIES

In past columns, I've written about topics mostly related to the shop floor, including (1) data collection and the basic questions you can answer, (2)

Sagi Reuven

material management and its impact, and (3) data-driven decisions and micro-solutions in manufacturing.

In my September column, I planned to present a few micro-solutions for electronics manufacturing, but I've decided to "swim upstream" or simply to shift left. It is clear to everyone in the Industry 4.0 era that the holy grail is to close the loop between design and manufacturing.

Mergers and acquisitions of billions of dollars were initiated to support this vision. In this column, I will talk about design for manufacturing (DFM).

To read the full column, click here.

Sagi Reuven is a business development manager for the electronics industry, Siemens Digital Industries. Download your free copy of the book *The Printed Circuit Assembler's Guide to... Advanced Manufacturing in the Digital Age* from Mentor, a Siemens Business, and visit 1-007eBooks. com for other free, educational titles. You can also view Siemens' free, 12-part, on-demand webinar series "Implementing Digital Twin Best Practices From Design Through Manufacturing."

## Master the art of keeping cool!

Learn how to beat the heat in your designs with techniques and methods from a fabricator's perspective.

## The Aerospace and Defense Chapter of the HIR

#### Feature Interview by the I-Connect007 Editorial Team

Nolan Johnson and Andy Shaughnessy recently spoke with Jeff Demmin of Keysight Technologies, who breaks down the work his team has done on the Aerospace and Defense Chapter of the Heterogeneous Integration Roadmap (HIR).

**Nolan Johnson:** Jeff, IEEE pointed us in your direction to discuss your chapter of the HIR. What's your background and involvement with the HIR?

**Jeff Demmin:** My background is broadly in semiconductor packaging. From 2015 to 2019, I worked for a company called Booz Allen Hamilton, which is a major government contractor. In that role, I supported leading-edge technical research related to packaging and heterogeneous integration, primarily at DARPA. I also have some background in the publishing world.

With my long career in packaging and my more recent experience specifically in the military and aerospace arena, I got tapped to work on the Aerospace and Defense Chapter of the HIR. I know most of the people involved in it, and I like to participate in industry activities, so it was an obvious match. Also, I want to be clear that my involvement is as the co-chair of this committee on the HIR and is not associated with my work for Keysight Technologies, nor does it represent the company's thoughts. I do this mostly in my spare time, which is probably true of many of the people participating.

I jumped in relatively early a few years ago, shortly after the HIR effort was begun. It was created to continue the work of the broadly used International Technology Roadmap for Semiconductors (ITRS), which had been around for a couple of decades, driving the node-based metrics for how the semiconductor industry should move ahead. But with Moore's Law running out of steam, mostly meaning that it's too expensive to keep it going, the HIR was one thrust that arose from the demise of the ITRS.

**Johnson:** The rationale makes sense. There may be a portion of your overall design that requires cutting-edge fabrication technologies but forcing your entire design to adhere to that

we are fully operational, and shipping your PCBs on-time!

the sun always rises

Jeff Demmin

just because you need it in one key section has always been onerous. This does give you the opportunity to flex with what's inside the package.

**Demmin:** The most obvious example of that, which has been recognized for a long time, is memory and processors. They use different fabrication processes. It's still silicon, digital, etc., but they're different processes just because of the nature of how they function. Splitting memory off from processors has been common for quite a while.

But all the other functions that end up in a big system-on-chip piece of silicon makes it quite inefficient to do it that way. Designers do everything they can to minimize the area's silicon usage. And if you can carve out something that doesn't need that leading node, that's a smart thing to do, but you need to put it all back together after you carve it up. That's the heterogeneous integration angle need that arises from this partitioning.

**Johnson:** Your target audience and the industry you're writing about have a reputation for

being fairly conservative. What would be the motivation for the mil-aero industry to jump into this technology?

**Demmin:** It's different depending on what industry you're in. One of the challenges is that the HIR effort covers everything from consumer to military. Companies that are on the digital high-volume side that are very supportive of this—such as Intel, AMD, and NVIDIA—can save a lot of money and create new capabilities if they can divide up their functions and then integrate them after the optimized manufacturing of each.

Xilinx was the first to divide up one of their big FPGAs, and they split it into four slices and put them on a silicon interposer that connected them together. Nowadays, that's pretty common to do something like that; companies like Intel are integrating different kinds of devices—not just the same device divided into more manageable chips. There's a lot of interest in heterogeneous integration of processors, data converters, memory, ASICs, and even optical components now.

On the military side, in spite of what people might envision as unlimited funding for military stuff, that's not really the case—especially when the volumes are low, and you don't have the total volume driver as you do in cellphones to amortize design, mask, and fab costs. Having those same kinds of savings, while still mixing and matching the best types of devices for different functions, offers that benefit for the aerospace and defense world.

It has even more challenging because there would commonly be a wider variety of devices potentially in a radar system or defense communication or electronic warfare where you need to be able to put together silicon, gallium arsenide, indium phosphide, and gallium nitride, among other device types to get the best possible performance. Challenges are conceptually similar in military and aerospace, but there are typically more types of devices for these specialized applications.

**Johnson:** What was your team's process for putting together the chapter?

**Demmin:** Tim Lee of Boeing is the other cochair, and he started on this before I did. The roadmapping process is especially tricky for heterogeneous integration, where there are so many variables. It doesn't always work to have the node-drive tables and metrics as had been in the ITRS. There are different types of devices, applications, design processes, and materials. There are so many more variables that couldn't replicate what had been done before on roadmaps.

The aerospace and defense chapter starts with a landscape of what people are doing. That meant compiling information on government efforts in this area, as well as some industry capabilities. Step zero of a roadmap is to have a starting point. The initial release of the chapter last year was more like a landscape, such as, "Where do things stand now? What are some of the activities underway?" It wasn't as much of a prescriptive roadmap of what we're projecting to be in place, but we will be working toward that in future editions. The process moving forward will follow the same practice as the ITRS, with alternating years of totally new versions and more modest updates in years in between. We're due for an update with some changes.

For the 2020 update after the inaugural 2019 edition, we put together a high-level table that looks more like a roadmap but still needs input to populate the various topics into the future. We broke it up into some different areas of performance, metrics, design processes, integration technologies, and segments of reliability. For these heterogeneous systems, reliability has not been thoroughly thought out and captured. There are all kinds of standards for single chips and packaging. There are different approaches that are still in the works.

One example that highlights how A&D is different from commercial and consumer products is the supply chain. That's one of the big differences between aerospace and defense compared to the product areas covered in the HIR. It's just a matter of security requirements throughout your supply chain, but it also requires obsolescence management in A&D because product lifetimes are often longer than the typical lifetime of devices within it. That's much less of an issue for commercial products where there are multiple suppliers, and you are churning new designs routinely that incorporate whatever the latest available devices are.

One new development that we expect to help the HIR is high-level interest and funding in semiconductor manufacturing from the U.S. Government. You've probably seen a couple of different bills in Congress and the Senate. They represent an enormous level of funding-at least \$25B—for the semiconductor industry in the U.S. Clearly, it's focused on manufacturing, which is a notable change and a good addition to the DARPA-style research targeting breakthrough technologies. Also, it's very broadly based, with funding via the NSF, Department of Energy, and Department of Commerce—not just the DoD. There are efforts to create interposer-based heterogeneous integration facilities in the U.S., for example, rather than relying on off-shore capabilities.

#### One example that highlights how A&D is different from commercial and consumer products is the supply chain.

**Johnson:** You do have a bit of interposer design and manufacturing required for heterogeneous integration.

**Demmin:** It's just interconnect on the interposer, so theoretically, it's easier than fabricating leading-edge devices. People have even tried things like having just a layer or two for customization in your interposer design above standard pre-fabricated power and ground planes. It's not quite as efficient for performance or design, but you can do it faster. As volumes increase, I can see some novel approaches like this facilitating adoption by reducing cost and turnaround time.

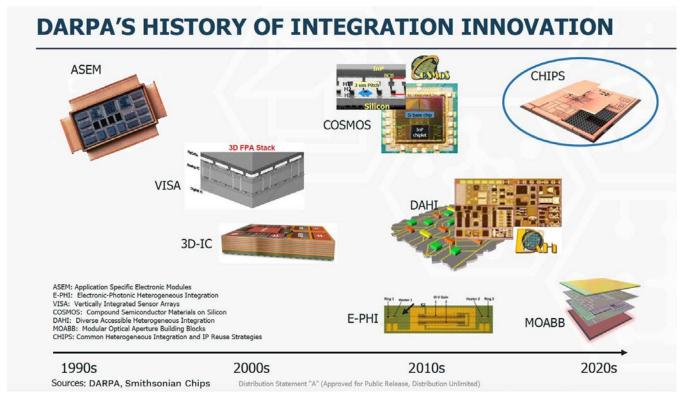

In DARPA's CHIPS program, part of the output was some very advanced designs and integration schemes, but getting those interposers manufactured and devices assembled was difficult because those capabilities aren't really available on a merchant basis in the U.S. Another output from the CHIPS program was a "wish list" for a national capability for interposer-based assembly.

This was input into the SHIP program. SHIP is a Naval Surface Warfare Center program for "State-of-the-Art Heterogeneous Integrated Packaging." This program is underway, and all of the detailed specifications and metrics for the SHIP program will be very helpful for the HIR.

**Johnson:** There is a lot of implied impact on PCB fabrication and assembly down the line as heterogenous integration becomes more prevalent.

**Demmin:** Definitely. All the advanced R&D like at DARPA is necessary, but a lot of it comes back to the PCBs for the advanced package substrates. That's where the rubber hits the road. The large volume of everything depends on the circuit board.

DARPA frequently uses a slide that shows that the PCB is the original heterogeneous integration platform, and it arose out of the need during World War II for a proximity fuse. They needed to get a lot of functionality within the small device, and the first high-volume PCB was the answer. The most advanced packaging substrate is conceptually no different from that PCB from 75 years ago.

**Johnson:** Do you have some specific feedback you'd like to hear from industry participants?

**Demmin:** We have a few others besides Tim and me, but we'd appreciate anyone who can help with informed input. To provide some focus, I've sent them this table, asking them to provide inputs on whether there should be other rows and get their input on what they think is state of the art, what they think it should be, and where it's headed. We're theoretically doing a 5-, 10-, and 15-year outlook, and it might be useful to have more granularity. Feedback on this table is the main thing I've asked for from other volunteers and the audiences of these presentations.

**Johnson:** Thank you very much, Jeff.

Demmin: Thanks. SMT007

Editor's note: To learn more, read Demmin's article "The Heterogeneous Integration Roadmap for Aerospace and Defense" on page 32 of this issue.

#### **NEW DATES ANNOUNCED!**

**Meetings & Courses:**

March 6-11

**Conference & Exhibition:**

March 9-11

SAN DIEGO CONVENTION CENTER | CA

GG TECHNICALLY C SPEAKING:

### IT'S THE PLACE TO

IPC APEX EXPO 2021 will be packed with far-reaching ideas and insights.

**Denise J. Charest** Quality Engineer,

Quality Engineer, Amphenol Printed Circuits

IPC APEX EXPO 2021 is proceeding as an in-person event. IPC and the San Diego Convention Center are committed to the well-being and health and safety of all attendees.

Feature by Jeff Demmin KEYSIGHT TECHNOLOGIES

#### 1. Summary

#### Semiconductor Roadmap History

Most people in the semiconductor industry are familiar with the International Technology Roadmap for Semiconductors (ITRS), which provided guidance for the industry starting in 1991 (as the National Technology Roadmap for Semiconductors). As the benefits of Moore's Law became more difficult and more expensive to achieve, the organization decided to publish a final version in 2016. The baton was handed to the Heterogeneous Integration Roadmap (HIR), with the realization that heterogeneous integration—assembling different types of devices rather than monolithic fabrication—is an important enabler for continued progress in the semiconductor industry [1].

The aerospace and defense segment of the semiconductor industry has unique needs in terms of technology, security, supply chain, and lifecycle. Heterogeneous integration is a critical technology that intersects all of these challenges, so the HIR organization identified aerospace and defense (A&D) as one of

the topics to have a chapter and a technical working group (TWG) that specifically targets the unique requirements of aerospace and defense. The HIR identifies challenges in 5-, 10-, and 15-year horizons and provides guidance on how to meet those challenges. This is, of course, a perpetual work-in-progress and will be updated as capabilities move forward and new requirements arise.

#### **Initial Scope**

The initial version of the A&D chapter published in 2019 is focused largely on challenges and requirements for the U.S. Aerospace and Defense Industry. The intent of the HIR is to create a document that provides guidance that is useful to the semiconductor community around the world, so the U.S.-centric viewpoint should be seen as just the starting point for this work. There are certainly many technical challenges that are pervasive throughout the international A&D industry, such as reliability, bandwidth, thermal management, radiation hardening, long product development cycles and lifetime, and supply chain security, so much of the content can be generalized beyond the U.S. aerospace and defense industry. Future revisions of this chapter will reflect that broader scope.

## Experience the Blackfox Difference!

#### **Premier IPC Training & Certification**

- High quality training and customer service

- Offering 6 certification programs at 6 locations and online

- Colorado, Arizona, Guadalajara & Queretaro, Mexico, Malaysia and Singapore

- Military Veterans Advanced Manufacturing Program

- IPC/WHMA-A-620 Space Addendum for trainers and specialists

- Online store supporting the training industry

for Limited 1-Person and

Training

For more information contact us at 888.837.9959 or sharonm@blackfox.com

www.blackfox.com

#### 2020 Update

The 2020 updates to the A&D chapter in the 2019 edition include: (1) updates on government-funded heterogeneous integration programs, (2) recent relevant market data, and (3) the 0.1 version of the A&D Roadmap table. Populating and refining the table in Figure 10 will be the focus of the 2021 edition of the HIR.

#### 2. Government Investment in Heterogeneous Integration

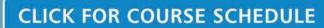

#### DARPA's DAHI Program

The U.S. Government, and DARPA specifically, has a long history of investing in heterogeneous integration. Figure 1 shows a timeline of these investments, which were often focused on specific applications and structures. The recent Diverse Accessible Heterogeneous Integration (DAHI) program was a large effort that demonstrated HI for a wide range of devices, with fine-pitch interconnect for breakthrough performance and capabilities. Figure 2 shows the progression during the DAHI program. This work helped to shape

initial thoughts for the HIR A&D effort, and the metrics tables for DAHI and other programs provide useful inputs for roadmapping efforts.

#### DARPA'S CHIPS Program

Following DAHI, DARPA's Common Heterogeneous Integration and Intellectual Property Reuse Strategies (CHIPS) program worked to establish a standard interface and promote IP reuse in a "chiplet" ecosystem designed to make heterogeneous integration more practical. This vision is shown in Figure 3, and the program metrics are shown in Figure 4. One significant outcome of CHIPS was a demonstration by prime contractor Intel and its partners of an Intel FPGA integrated with leading-edge data converters, an optical device, and other chips using its Advanced Interface Bus (AIB), the interface standard selected in the CHIPS program.

One outcome of the CHIPS program was the quantification of the interposer-based heterogeneous integration manufacturing requirements, which have been lacking on a merchant

Figure 1: DARPA has a long history of guiding and investing in heterogeneous integration [2].

#### DAHI simplicity enables rapid evolution

| Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MPW0           | MPW1                        | MPW2                        | MPW3                     | Future MPWs                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|-----------------------------|--------------------------|-----------------------------|

| смоѕ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IBM 65nm       | GF 45 nm                    | GF 45 nm                    | GF 45 nm                 | GF 45 nm                    |

| InP HBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TF4 (2 metals) | TF4 (3 metals)              | TF4 (4 metals)              | TF4 (4 metals)           | TF4 (4 metals)              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | TF5 (3 metals)              | TF5 (4 metals)              | TF5 (4 metals)           | TF5 (4 metals)              |

| InP Varactor<br>Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                             |                             |                          | AD1                         |

| GaN HEMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GaN20          | GaN20                       | GaN20                       | GaN20                    | GaN20                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T3 (HRL)       | T3 (HRL)                    | T3 (HRL)                    | T3 (HRL)                 | T3 (HRL)                    |

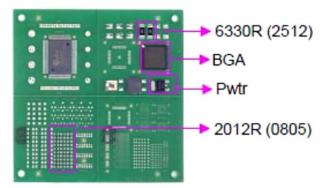

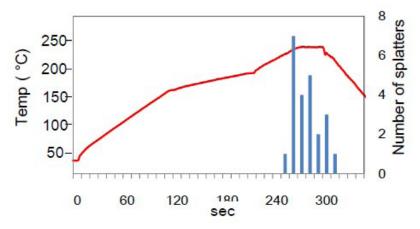

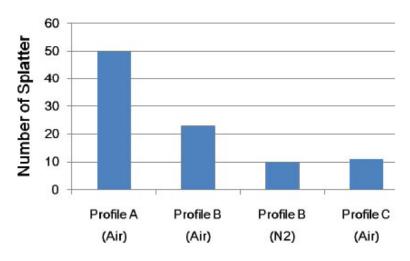

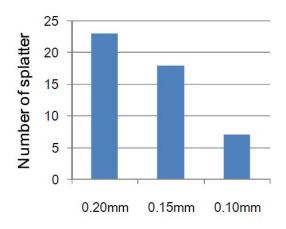

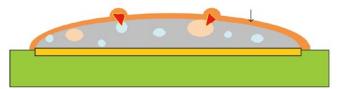

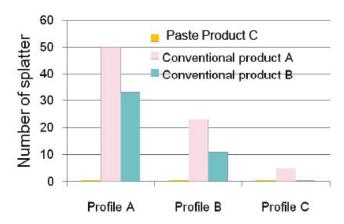

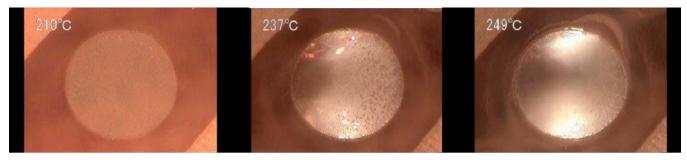

| GaAs HEMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                             |                             | P3K6                     | P3K6                        |